# 高速信号伝送技術: Synfinity II

## **High-Speed Signal Transmission Technology**

#### あらまし

Si集積回路の高性能化に伴い集積回路チップに出入りするデータ量は増加する。チップ入出力のデータ転送能力がチップ性能に見合って向上しなければ、これが性能のボトルネックになる。このボトルネックを解消するための回路技術側からの解答が、高速信号伝送技術である。

本稿では高速信号伝送技術が今後どのような要求に応えなければならないかを述べた後,バンド幅2.5 Gバイト/秒のサーバ間接続技術(Synfinity II)向けに開発してきた回路技術を紹介する。

#### **Abstract**

Due to the tremendous increase in Si LSI performance, the amount of data that can be input to or output from an LSI chip has sharply increased. However, if the inter-chip data transmission capacity is not sufficiently improved to keep up with the intra-chip data processing capacity, the total data processing capacity will be restricted. This problem can be resolved by a new high-speed signal transmission technology.

This paper describes the future demands on this transmission technology and introduces a new inter-server connection technology to be used in Synfinity II that provides a bandwidth of 2.5 gigabytes per second.

田村泰孝(たむら ひろたか)

1982年東京大学大学院工学系研究科 了。同年(株/塩土)通研究所入社。以 来ジョセフソン集積回路などの超低 専寮子・回路の研究に従事。1996年 よりCMOS回路設計の研究を開始, 現在に至る。 システムLSI開発研究所

後藤公太郎(ごとう こうたろう)

1988年早稲田大学大学院理工学部電気工学科修士課程了。同年(株)富士 通研究所入社。以来SQUID健康計な どのジョセフソン集積回路の研究に 従事。1996年よりCMOS回路設計の 研究を開始,現在に至る。 システムLSI開発研究所先端システム Raghu Sastry (ラグー・サストリー)

1994年University of South Floridaよ りComputer Scienceの学位(Ph. D. )を 取得。同年HAL Computer System, Inc. 入社。Design managerとして VIS1設計に従事。IEEEの論文誌およ び会譜への採択論文が18件あり,米 国特許5件を保有している。

## まえがき

Si集積回路の性能は過去30年以上にわたってMooreの 法則<sup>(1)</sup>に従った向上を続けてきた。現在(1999年) たその性 能向上は続いており, Si(特にCMOS) 集積回路を用いた 情報処理システムは,構成要素レベルにおいてもシステム全体のレベルにおいても高い成長率で性能が向上しつ つある。

集積回路チップの中で処理される情報の量が増大すれば,必然的にチップに出入りするデータ量も増大する。 もしチップ入出力ピンのデータ転送能力がチップ性能向上に見合って増加しなければ,入出力がチップ性能のボトルネックになるだろう。筐体レベルのシステムについても,システム性能の向上に見合う入出力チャネルの速度向上がなければ,入出力がシステム全体のボトルネックになる。

本稿では、高速信号伝送技術の予測を紹介した後、著者らがHAL Computer System, Inc. と共同開発してきた信号伝送技術に関してその概要、要素回路技術を紹介する。

## 高速信号伝送技術の重要性(2)

この章では,チップ間信号伝送に関する将来予測を紹介する。この予測はMooreの法則に代表されるトレンドに基づいている。予測に無批判にトレンドを用いることは危険を伴うが,十数年以内の予測に限ればある程度確からしいと考えてよいだろう。少なくともこの先十数年程度についてはMooreの法則を成立させるだけの技術的蓄積があるからである。

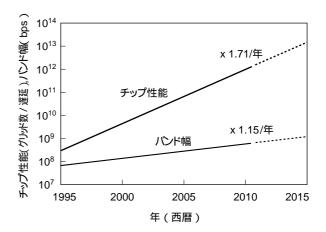

Mooreの法則によればCMOS集積回路の性能で、ゲート数 × クロック周波数)は年率71%で増加する。これと同じペースでチップのパンド幅、チップと外部との総情報転送量)を増加させるのは非常に困難であるが,何らかの方法で性能とパンド幅のギャップは埋めなければならない。年率71%という値は力づくの手段で達成するにはあまりに大きく,材料・デバイスから回路,システムを含む総合的な対策が必要になる。

まず材料,デバイス上の工夫であるが,これは材料の 改善(Cu配線や低誘電率絶縁層の使用など)やトランジス 夕性能の向上によりトレンドに乗った速度向上を達成す ることに尽きる。その目標は,集積回路のピン当たりの データ転送レートをトランジスタ速度の増加率15%/年で 増加させることである。それでも年率49%(1.71/1.15 = 1.49)という増加率でチップ性能とバンド幅のギャップは 開いていく(図-1)。

図-1 LSI**の性能とピンパンド幅の予測** Fig.1-Scaling of LSI capability and pin bandwidth.

この差を埋める手段の一つは、ピン数をピンピッチの縮小とチップサイズの増加により増やしていくことである。トレンドどおりにいけばピン数は年率約11%で増加できる。したがって、コスト増加を気にせずピン数を増大できる場合にはチップ条件でのバンド幅の成長率を年率28%まで上げられる。それでも性能とチップバンド幅の間のギャップは年率34%(=1.71/1.28)で増加していく。この残されたギャップに関しては回路とシステム上の工夫で解決する必要がある。

システム的な対策としては、チップ性能の向上がそのままパンド幅増加に結びつかないように工夫することが挙げられる。チップ性能とパンド幅Bの関係に関してはRentの法則と呼ばれる経験則<sup>③</sup>が知られており

$$B = K_{D}C$$

· · · · · · · · (1)

が成り立つ。ここでKRは比例定数,Cは性能グリッド数/ゲート遅延)である。指数 はデータの局所性 (locality)を高める特別の配慮をしないチップでは0.5から 0.75の範囲となり,典型的には0.7程度になることが知られている。指数 の値として0.7を採るとチップバンド幅 Bの増加率は年率46%となり性能成長率71%よりは小さな値に抑えられるが,それでも高い値であることに変わりはない。

システム側では比例定数K<sub>R</sub>と指数 を小さくしチップ 外部との情報交換ができるだけ小さくなるようにする必 要がある。

回路的な対策は,現在チップ内信号転送より低い周波数で行われているチップ間信号転送速度を上げ,チップ内よりむしろ高い周波数に移行することである。しかし,現在高々数百 MHzであるデータ転送速度を10倍の数GHzと向上させたとしても,それが一回きりの増加であ

れば5-6年の内にこれで生じた余裕は年率46%の要求バンド幅増加により食いつぶされる。つまり再びバンド幅ボトルネックに直面する。移行後もピンの速度をトレンドどおり増加(15%/年)すればボトルネックに直面するまでの期間を10年程度に伸ばすことができる。この期間を用いて長期的な対策,すなわちチップ外との情報のやりとりができるだけ小さくなるようなアーキテクチャへの移行を行えばよい。例えば、Rentの法則の指数を0.4程度まで低下させるアーキテクチャに移行できれば、ボトルネックに直面するまでの期間は30年となり、通常の感覚からすればバンド幅ボトルネック問題は解決されたと言ってよい。

以上述べたように、チップの性能とバンド幅のギャップが広がっていくことは、将来の集積回路技術にとって極めて深刻な問題・バンド幅ボトルネック・をもたらす。しかし、この問題は材料・デバイス技術に加えて回路からシステムまでのあらゆるレベルで対応すれば解決可能である。言い換えれば、この問題は将来の新しい回路技術、アーキテクチャを生み出す原動力となる可能性を持っている。例えば、DRAMとlogic混載を前提とした様々な新アーキテクチャ提案などもバンド幅ボトルネックの回避という流れの中に位置付けられる。高速信号伝送技術もこのような技術の流れの中で現れてきたということを強調しておきたい。

#### Synfinity II 高速信号伝送技術

Synfinity II 高速信号伝送技術の概要(4)

ここで高速信号伝送技術の一例として,著者らのグループがコンピュータ事業部およびHAL Computer Systems, Inc. と共同で開発を行っているSynfinity II<sup>(4)</sup>を紹介する。

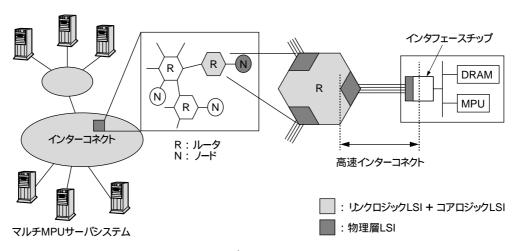

Synfinity IIはマルチプロセッサ間の相互接続(インターコネクト)を主なターゲットとして開発が進められている。Synfinity IIにより低コストのマイクロプロセッサを多数接続して高性能のサーバが実現される(図-2)。プロセッサ間は一方向あたり最高2.5 Gバイト/秒(20 Gbps )のバンド幅を持つ双方向リンクで接続される。リンクの物理的形態は1対1接続を基本としているが、6 ポートのルータチップ(スイッチ)を使うことで多数のプロセッサエレメントやメモリ間を相互接続する網目状のネットワークが形成される。

Synfinity IIで用いられるネットワークは,ほかの通信ネットワークと同様に種々のハードウェア・ソフトウェアを含む階層構造からなっている。本稿では,そのうちで実際にケーブルに信号を送受信する物理層 (physical layer)の回路技術を説明する。

物理層の信号伝送路(物理リンク)はデータ幅が2パイトの双方向リンクであり、データ線1本あたりの信号伝送速度は最大1.25 Gbpsである。信号伝送には銅ケーブルを用いた差動伝送を使う。小さなシステムでは信号伝送は同一プリント基板上に限定されるが、より大きなシステムでは筐体内や筐体間でパックプレーン接続、あるいはツイストペアケーブルを用いて信号を伝える。Synfinity IIの物理リンクは同一の回路でプリント基板上の接続から筐体内接続、筐体間接続までをカバーする。

Synfinity IIの物理リンクは以下のような特徴をもって いる。

### (1) 高パンド幅

一方向あたり2.5 Gバイト/秋(20 Gbps)で差動信号線 1 対あたり1.25 Gbpsの信号を2バイト(16ピット)幅で伝送 する。双方向通信のためこのようなリンクを上りと下り

図-2 サーバ用インターコネクト Fig.2-Interconnect for multi-processor server system.

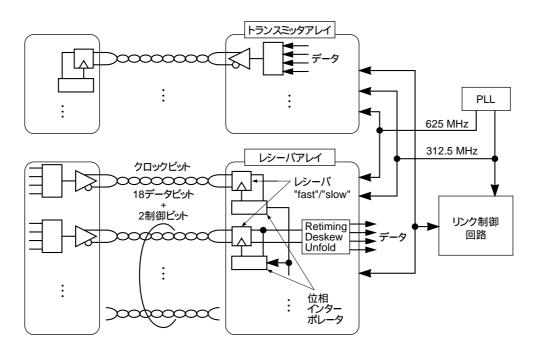

図-3 Synfinity II用トランシーバの構成 Fig.3-Synfinity II transceiver architecture.

で1組ずつ持ち,上り下り合計で1リンクあたり40 Gbps のパンド幅となる。またリンクとの接続ポートを6組持つルータは全体で240 Gbpsという大きなパンド幅の信号を入出力することができる。

#### (2) 低レイテンシ

マルチプロセッサ間の信号伝送においては、ほかのプロセッサノードの下にあるメモリへのアクセスがリンクを通じて行われる。リンクが性能ボトルネックとならないためには、そのレイテンシ(遅延)をできるだけ小さくする必要がある。Synfinity IIではトランスミッタ、レシーバ、同期回路からなる物理層(ケーブルを除く)は約6nsという低いレイテンシを達成した。

#### (3) 伝送線路特性に応じた伝送速度の選択機能

伝送線路の品質が悪い(例えばケーブルが長く信号の減衰が大きい)場合には必要な伝送品質が得られるまで伝送レートを下げる機能がある。最高レート1.25 Gbpsに加えてその1/2,1/4,1/8と4種類のレートをサポートする。送信回路(トランスミッタ)の送信レベルはケーブル品質,周波数に応じて自動調整される。

#### (4) 信号線間skewの自動調整

レシーバは,パラレル伝送の信号線間の遅延時間の違い(skew)を調整する機能を持つ。調整できるskewは最大でピットセル幅 T の 8 倍(1.25 Gbps伝送時で6.4 ns)である。skewの調整機能があるため,信号線間skewをなくすためのケーブルトリミングなどの処理を行う必要がない。

#### (5) 最大ケーブル長20 mをサポート

信号伝送レートが1.25 Gbpsでは 5 mまでのケーブルを用いる。半分のレート612.5 Mbpsではケーブル長を20 mまで伸ばすことができる。20 mのケーブルの中で信号の高周波成分が減衰することを補償するため,受信回路側にイコライザ回路を持つ。

#### トランシーバのアーキテクチャ

物理リンクに用いる送受信回路(トランシーバ)の構成を図-3に示す。トランシーバは送信器(トランスミッタ)と受信器(レシーバ)それぞれ21個から成っている。21個の送受信器のうち1組はクロックの伝達のために使われている。残りの20ビットのうちデータが18ビット(2×8ビットとECCビットが2ビット),残り2ビットは制御コードである。

Synfinity IIは送信側と受信側でクロック周波数のわずかの差(水晶発振子の誤差)を許容する仕様となっている。このため、データと一緒にクロックを送り、受信側で送信側のクロックをリカバリしてレシーバを駆動する。クロックを送受信するトランスミッタとレシーバはデータ送受信用のものと全く同じである。

なお,送信されるクロックは,データ1と0を交互に送ったものと等価であるためデータレートの半分の周波数となる。

クロック用のレシーパは送られてきたクロック(受信クロック)を内部クロックに同期してサンプリング・判定す

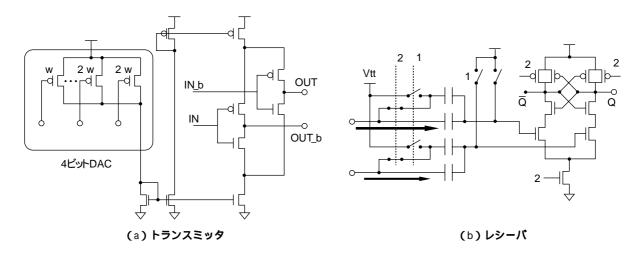

図-4 トランスミッタおよびレシーバの回路構成 Fig.4-Transmitter and receiver circuit schematics.

ることでの両者の位相を比較する。この情報をもとに内部クロックの位相が調整される。位相調整には受信クロックに位相同期して位相を際限なく増加あるいは減少させることができる回路(位相インターポレータ)を採用した。この調整により内部クロック周波数は受信クロックに同期することになる。

データ受信用のレシーバを駆動する内部クロックもクロックレシーパで取得される位相情報を基に位相の増減を行う。したがって,データ受信用レシーパのクロックも受信クロックに位相同期する。

各レシーバを駆動する内部クロックの位相初期値は、eyeの中央でデータをサンプリングするように選ばれている。初期値の調整はリンクのリセット後のイニシャライズ期間に行われる。イニシャライズ後は各レシーバの内部クロックはクロックレシーバからの位相情報に基づき変化していく。データも受信クロックも同一チップ上の同一種類のドライバから送られているため、初期状態でレシーバがeyeの中央でデータをサンプルしていればその後もeyeの中心でデータをサンプルし続ける。

信号線間にskewがあっても、レシーバのそれぞれがデータeyeの中央でデータをサンプリングし続けることにより、Synfinity IIの特徴の一つであるskew調整機能が実現される。クロック位相の初期値を調整することによるskew補償の範囲はビットセル幅Tであるが、後段にビットセル幅Tの整数倍のskewを調整する回路を設けているので、最大8Tまでのskew調整が可能である。

#### トランスミッタ

トランスミッタは、4対1のパラレル・シリアル変換を 行いコアクロック周波数の4倍のピットレートで信号を 伝送する。トランスミッタの出力段はpush-pullの定電流 ドライバとなっており,その出力を線路の特性インピーダンスZOで並列終端している{図-4(a)。 トランスミッタの出力振幅は4ビット分解能のD/Aコンバータにより制御され,最大±8mAの電流をチップ外の負荷に出力できる。

4対1のパラレル - シリアル変換のためにコアクロック(312.5 MHz )に同期した4相クロックを用いた。コアから4ビット並列にデータを供給し,隣り合う位相のクロックの立ち上がリエッジ間の期間に並列データのうちの1ビットが出力段から出力される。

高速信号伝送に用いるレシーバは、信号伝送に用いられる数百mVの信号振幅を通常の論理回路が扱える数Vまで増幅する必要がある。通常の増幅器ではゲイン・バンド幅積が一定になるため、高いゲインを得ると帯域が制限され必要な応答時間を得るのが難しい。そこでSRAMのセンスアンプなどにも用いられている再生型ラッチを用いている。

信号伝送レートが1Gbps以上の領域になると,ケーブルの表皮効果損失などにより信号の高周波成分が減衰する。この減衰により時間的に前後する符号間で干渉(ISI: Intersymbol Interference)が生ずる。

ISIの効果を補償するためSynfinity IIではレシーバ側で容量ネットワークを用いたイコライズを行っている。容量ネットワークによるイコライザを持つ再生型ラッチの回路例を図-4(b)に示す。⑤

#### 位相インターポレータ

各レシーバを駆動する内部クロックは位相インターポレータで発生する。位相インターポレータはクロック受信回路が発行するUP/DOWN信号を積分して対応する位

相を出力する。この積分はディジタル的にカウンタで行われるため,アナログ的な積分回路のような積分時間の制限はない。

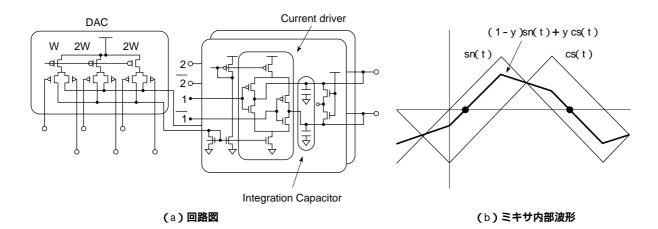

位相インターポレータという名称は、4相クロック(位相間隔が90度)から補間(インターポレーション)により中間位相を作る動作を行うことから付けられた。回路の中心部分は差動積分回路からなる4象限ミキサ{図-5(a)}である。4象限ミキサは入力クロックを矩形波電流に変換し容量で積分することで三角波を作る。隣り合う位相のクロックに対しそれぞれ異なる振幅の矩形波電流を発生させて積分容量で積分すると、それぞれの三角波の重み付き和に相当する電圧が容量に発生する{図-5(b)}。

このようにして発生した差動信号がゼロ交差する時刻は、重みを第一の位相のクロックから次の位相のクロックに移していくことにより、連続的に第一の三角波のゼロ交差時刻から第二の三角波のゼロ交差時刻まで変化する。ゼロ交差を差動コンパレータで矩形波に変換すれば、立ち上がリエッジの位置が 0-360度の間で制御できるクロックが発生する。

位相インターポレータは出力クロックの位相を25 ps分解能で設定でき、出力の理想的な位相・コード特性からのずれは最大で±10 ps以下であった。これは、1.25 Gbps-2.5 Gbpsの信号伝送のためのクロック発生回路として十分な性能である。

#### PLL回路

レシーバの位相インターポレータおよびドライバへの クロックはPLLから供給される。PLLには差動遅延段を用 いた4段VCOを用いた。高速信号伝送においてはクロッ クのjitterをできるだけ小さくすることが求められる。 PLLにjitterが生ずる大きな原因の一つは電源電圧の変動 によるVCO発振位相の変動であるが、この影響を低減するため内部降圧電源を用いて電源電圧を安定化している。

#### リンク制御回路

リンク初期化やクロックリカバリ状況の監視など物理 層固有の様々な制御は物理層に内蔵された制御回路に よって実施される。このため上位の層は物理層の動作の 詳細を知る必要はなく,またその制御を行う必要もない。

リンク初期化のプロセスでは,通信相手のクロック周波数の確認,デバイスIDの交換,クロックリカバリの確立,トランスミッタ出力振幅の最適化を自動的に行う。物理層は0101・・・の周期波形,000010000などの孤立パルス,疑似ランダム波形を用いて安定な信号送受信を行えることを確認した後で,リンクreadyの信号を上位層に与える。物理層から信号を受け取る上位層は最初にリセット信号を送るのみであり,あとは物理層がリンクreadyの信号を出すのを待ってから実際の通信作業に入る。

#### 実験結果

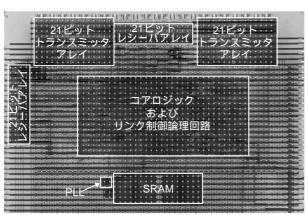

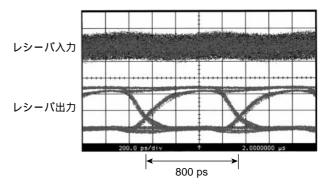

0.24 µ m CMOSプロセスで試作した物理リンクの transceiverのチップ写真を図-6に示す。芯線径AWG28の ツイストペア線20 mを通して1.25 Gbpsで伝送が可能であった。このときのレシーバ出力で見たeyeパターンを 図-7に示す。またケーブル長 5 mで1.25 Gbps伝送時の BER( bit error rate )は10<sup>-13</sup>以下であった。

#### 高速信号伝送技術の将来像

以上紹介したSynfinity II技術は,1-2パイト幅のパラレル伝送で信号線1本あたりGbpsクラスの信号伝送技術としては業界でトップレベルのものである。しかしこの分野の進歩は速く,研究開発のレベルでは1999年時点で2.5 Gbpsの1ビット幅伝送(シリアル伝送)ができることが

図-5 位相インタポレータ用4象限ミキサ Fig.5-Quadrature mixer for phase interpolator.

21ビットトランスミッタアレイ : 3,300 × 1,940  $\mu$  m<sup>2</sup> 21ビットレシーバアレイ : 3,300 × 900  $\mu$  m<sup>2</sup>

#### 図-6 **試作トランシーバのチップ写真** Fig.6-Transceiver chip photomicrograph.

当然視されている。いずれはSynfinity IIのようなパラレル 伝送でも信号線あたり2.5 Gbps ,5 Gbpsとデータレートを 向上させていく必要がある。

信号線あたりのシンボル伝送速度が数Gシンボル/秒以上になると表皮効果損失による信号減衰が著しい。したがって,そこから先はシンボル伝送レートを上げずにデータレートを増加させる工夫が必要になる。例えば,学会発表された10 Gbps伝送<sup>(6)</sup>では1シンボルで2 ビットを送る多値伝送を行うことにより,5 Gシンボル/秒の伝送で10 Gbpsを実現している。ほかの可能性としては1本の信号線に双方向に信号を送る双方向伝送がある。この場合も実効的に信号線1本あたりのデータレートを倍にできる。多値伝送と双方向伝送を組み合わせることは原理的に可能であるため,現状で20 Gbps程度までの技術的可能性は見えている。

## むすび

本稿では,電気的な信号をプリント基板上配線や銅線 ケーブルを通して伝える高速信号伝送技術について述 べた。

高速信号伝送技術が重要な理由は,集積回路およびシステムの情報処理量が年とともに指数関数的に増加していることによる。集積回路の性能が年率71%で増加するのに対し,チップに情報を入出力するレートはこの増加率では増えないため,入出力のバンド幅ボトルネックが生ずる。このボトルネックを改善するためには材料・デバイス,回路,システムにわたる総合的な対策が欠かせない。高速信号伝送技術はもっぱら回路技術の面からバ

(伝送速度: 1.25 Gbps)

図-7 レシーパ出力eyeパターン( 芯径AWG28 , 長さ20 mの ツイストペア線伝送 )

Fig.7-Eye diagrams.

#### ンド幅ボトルネックの解消に寄与するものである。

高速信号伝送技術の一例として,サーバ間相互接続を目ざして開発中のSynfinity IIに用いられている回路技術を紹介した。Synfinity IIには高速信号伝送に必要な要素,つまりクロックリカバリ,高速トランスミッタ回路および高速レシーバ回路,ビットあたりのskew調整技術などが含まれている。今後,著者らはSynfinity IIの技術を基に,より高速のインターコネクト技術や高速シリアル伝送技術を支える回路技術の開発を行っていく予定である。

#### 参考文献

- (1) G. Moore: VLSI: Some Fundamental Challenges. *IEEE Spectrum*, 16, p.30(1979).

- (2) W. J. Dally and J. W. Poulton: Digital Systems Engineering, Cambridge University Press, 1998.

- (3) B. Landman and R. L. Russo: On a Pin vs. Block Relationship for Partitioning of Logic Graphs. *IEEE Transactions on Computers*, C-20, 12, pp.1469-1479(1971)

- (4) K. Gotoh et al.: A 2B Parallel 1.25 Gb/s Interconnect I/O Interface with Self-Configurable Link and Plesiochronous Clocking. ISSCC Digest of Technical Papers, pp.180-181, February 1999.

- (5) H. Tamura et al.: Partial Response Detection Technique for Driver Power Reduction in High-Speed Memory-to-Processor Communication. ISSCC Digest of Technical Papers, pp.342-343, February 1997.

- (6) R. Farjad-Rad et al.: A 0.4 μm CMOS 10-Gb/s 4-PAM Pre-Emphasis Serial Link Transmitter . 1998 Symposium on VLSI Circuits Digest of Technical Papers , pp.198-199(1998)