409 ナノスクラッチ試験による  $\text{Si}_3\text{N}_4/\text{Cu}$  薄膜界面の界面強度評価

横浜国立大学 ○赤井 武志[院] 濵谷 忠弘

于 強 白鳥 正樹

## 1. 緒 言

現在、LSI配線に代表される電子デバイスの多くが、基板上に多数の材料を薄膜として積層させた薄膜積層体である。薄膜の積層により性能の向上や小型化などが実現されているが、一方で高温プロセス時には異材間の熱膨張率の差に起因して界面上に大きな応力が発生する。その結果生じる界面はく離が信頼性の上で大きな問題となっている。そのため、界面強度を定量的に評価する必要性が出てきている<sup>(1)</sup>。現在最も一般的に使用されている界面強度評価試験法がスクラッチ試験法である。試験が非常に容易であるが、はく離発生時の荷重値により界面強度を評価するため表面の破壊の影響が含まれてしまうことや、はく離を検出できず表面の破壊を検出してしまうことなど問題は多い<sup>(2)</sup>。

しかし、界面強度の非常に小さな界面に対してスクラッチ試験を適用すれば、表面の破壊をほとんど伴わずに、界面はく離を発生させることができると期待できる。また、従来の荷重-摩擦線図の変化によるはく離検出ではなく、目視によるはく離検出を行うことで、確実にはく離を検出することができる。

そこで、本研究では、実際のLSI配線に用いられる  $\text{Si}_3\text{N}_4$  (パッジベーション膜) / Cu (金属配線) 界面を対象としてスクラッチ試験を実施し、得られたはく離荷重を用いて応力解析を行うことにより、はく離発生に必要な応力値を求めた。また、得られた応力値を他の界面強度評価法によって得られた値と比較することにより、その有効性についての検討を行った。

## 2. 試験条件

**2.1 試験機** スクラッチ試験は Nano Indenter XP (MTS Systems Corporation) を用いて実施した。圧子の先端曲率半径は  $15\mu\text{m}$  であり、試験開始から連続的に荷重を測定した。試験条件を Table 1 に示した。なお、はく離はマイクロスコープにより膜表面のスクラッチ痕を観察することにより検出した。

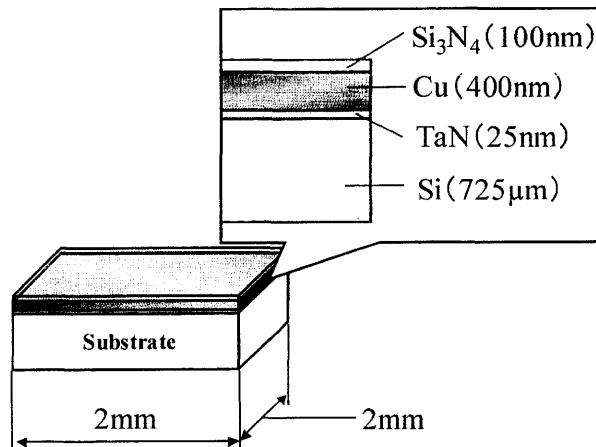

**2.2 供試材** 試験片の模式図を Fig.1 に示した。実際のLSI配線と同様にシリコン基板上にバリア膜としてTaNが製膜されており、その上に Cu (金属配線)、 $\text{Si}_3\text{N}_4$  (パッジベーション膜) が積層されている。2mm 角に切り出して試験片に供した。

Fig.1 Specimens

パッジベーション膜) が積層されている。2mm 角に切り出して試験片に供した。

## 3. 試験結果

試験後、膜表面のスクラッチ痕をマイクロスコープにより観察したところ、スクラッチ痕中に赤褐色の点が見られた。これは、はく離によって銅薄膜が酸化したことにより変色を起こしたものであり、この点で界面はく離が発生していると考えられる。このはく離発生点は荷重が大きくなると連続的に発生しているが、低荷重域では間隔をおいて局所的に発生していた。また、低荷重域ではき裂や割れなどの表面の破壊は観察されなかったため、純粹に界面はく離を発生させることができている。そこで、スクラッチ開始から最初に界面はく離が発生した点における荷重を測定したところ  $P=0.44\text{mN}$  であった。

## 4. FEM 解析

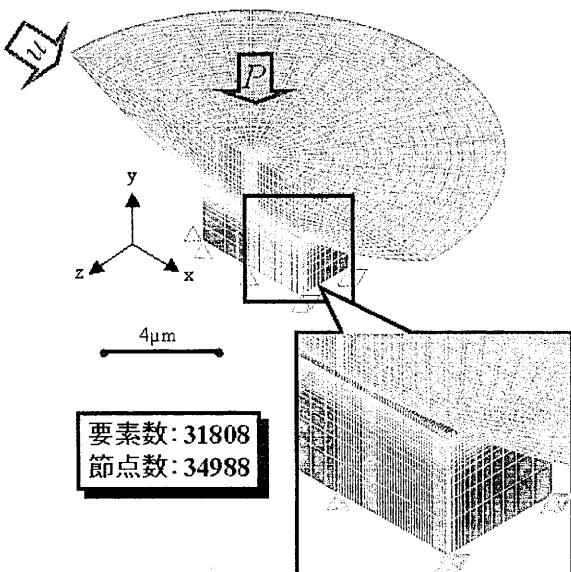

はく離発生時の界面上の応力分布を求めるため、解析ソフト Mentat/Marc を用いて応力解析を行った。解析モデルを Fig.2 に示す。解析は  $\text{Si}_3\text{N}_4$  と Cu の降伏および圧子と  $\text{Si}_3\text{N}_4$  薄膜の接触を考慮した三次元弾塑性接触解析である。垂直荷重は実験により得られたはく離荷重  $P=0.44\text{mN}$ 、水平変位は  $1\mu\text{m}$  である。

解析を行った結果、今回検出された界面はく離はせん

Table I Testing condition

| Scratch length   | Scratch velocity | Maximum load | Load velocity     | Delamination load |

|------------------|------------------|--------------|-------------------|-------------------|

| $200\mu\text{m}$ | $10\mu\text{m}$  | $5\text{mN}$ | $0.25\text{mN/s}$ | $0.44\text{mN}$   |

Fig.2 Analysis model

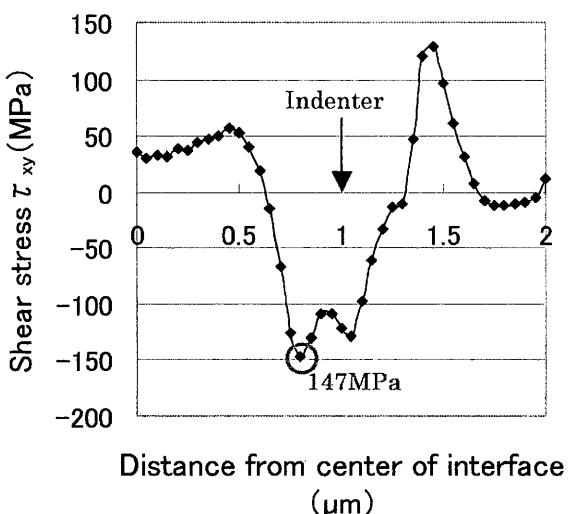

Fig.3 Stress distributions along the interface

断応力  $\tau_{xy}$  に支配されており、破壊形態はモードⅡ（面内せん断型）であることがわかった。そこで、界面上のせん断応力  $\tau_{xy}$  の分布を Fig.3 に示した。このグラフより圧子のやや後方において応力値が最大となっていることがわかる。つまり、この位置から界面はく離が発生したと考えられ、はく離発生に必要なせん断応力の値は  $\tau_{xy}=147\text{Mpa}$  であった。後方からのはく離であったために、はく離によってひずみにより蓄積された応力が開放されたために連続的なはく離ではなく局所的なはく離が発生したものと考えられる。

##### 5. 他のはく離試験との比較

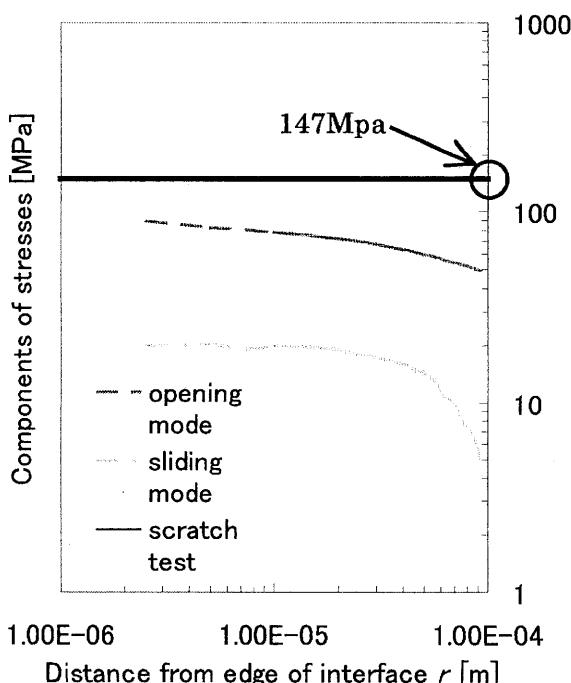

スクラッチ試験により得られた界面強度について検討するため、他のはく離試験として界面端はく離試験法との比較を行った。界面端はく離試験法は試験片にカンチ

レバーを取り付け、カンチレバーに荷重を負荷することで界面の端部からはく離を発生させることができる<sup>(3)</sup>。試験およびFEM解析によって得られた、はく離発生時の界面端付近の応力分布とスクラッチ試験によって得られたはく離発生時の応力値をグラフにしたものを作成した。前述したように、スクラッチ試験における界面はく離はせん断応力に支配されていることが分かっており、界面端はく離試験におけるせん断モード(Sliding mode)はく離試験に対応すると考えることができる。しかし、スクラッチ試験の結果は界面端はく離試験の結果に比べてはるかに大きな値を示している。この相違の主たる原因として、二つのことが考えられる。一つは薄膜を堆積させると必ず発生する内部応力の影響<sup>(4)</sup>、もう一つは界面端部（表面）付近の不安定な原子構造による界面強度の低下である。

##### 参考文献

- 1) 濵谷忠弘, 微細構造物としてのLSI配線の破壊機構に関する研究

- 2) 鴨志田武, PVD法による超硬質薄膜の製造技術, 茨城県工業技術センター研究報告 第21号

- 3) 濵谷忠弘, 鶴賀哲, 于強, 白鳥正樹, LSI用サブミクロン薄膜のモード別界面端はく離発生条件

- 4) 金原粲, 薄膜工学, 丸善株式会社

Fig.5 Stress distribution from edge of interface