# ナノスケール半導体デバイスにおけるヴァーチャルメトロロジー 技術を用いた最先端製造技術の実用化

Practical Application of Leading-Edge Manufacturing Technology using Virtual Metrology for Nano-Scale Semiconductor Devices

今 井 仲 一 安 田 哲 Shin-ichi Imai Satoshi Yasuda

#### 要旨

半導体デバイスに限らず工業製品の製造工程におけるインライン計測は,製品の品質確保のために必須であり,製造従事者にとって常識となっている。しかしながら,製品を全数計測することはコストの視点から不可能であり,コスト低減と品質向上を両立したモノづくりに革新する必要がある。

そこで,筆者らは,シリコン半導体デバイスの製造において製造装置のデータを利用して,ウェハ特性さらには電気特性まで予測するヴァーチャルメトロロジー技術を開発し,インライン計測のコストを付加せずに仮想的な全数計測による品質向上を,ナノスケールの半導体デバイスにおいて実証した。本技術は,製造工程の途中で特性を予測できるので,コスト低減だけでなく歩留まり向上を含めた,多くのメリットがある。

本論文では,半導体デバイス製造工程で最も重要なトランジスタ形成工程におけるゲート電極の閾値(しきいち)電圧を左右する,オフセットサイドウォール膜厚を成膜装置の変数によってナノレベルで予測し,さらに予測値を基に自動的に膜厚をフィードバック制御して,膜厚の工程能力指数Cpkが2.23の高品質の製造工程を実現した実例について紹介する。

#### Abstract

In the manufacturing processes of consumable products including semiconductor devices, in-line metrology is necessary to maintain high quality. In-line metrology is a common method for manufacturers. However it is impossible to examine all products by using in-line metrology. Innovative manufacturing technology which achieves high quality at low cost should be created. For silicon semiconductor manufacturing, we have developed Virtual Metrology (VM) and a Virtual Process Control Module (VPCM) using equipment variables, and we demonstrated the increase of quality in a nano-scale semiconductor device without additional inspection. These technologies have numerous merits since characteristics can be predicted in the fabrication process of a semiconductor device. This paper describes prediction of offset-sidewall thickness in the transistor fabrication processes and presents evidence of process capability index (Cpk) values up to 2.23 in offset-sidewall thickness using VM-APC (VM-Advanced Process Control).

# 1. はじめに

工業製品の製造工程では,抜き取りによるインライン計測が品質および歩留まり確保のため一般的に実施されている。ここで重要なことは,サンプリング頻度をどの程度に設定するかである。雑駁(ざっぱく)に言えば,不良発生確率の高い製品ではサンプリング頻度を高くして,不良発生確率の低い製品ではサンプリング頻度は低くする (注)。製造現場では,不良発生率は変化するのでサンプリング頻度は動的に最適化しなければならないが,実際は困難である。さらに,インライン計測は不良品を選別することによって市場への不良品の流出を防止しているので,見かけ上の品質と歩留まりを確保しているに過ぎず,根本的な品質および歩留まり向上は別途実施する必要がある。

したがって,理想のモノづくりでは不良品を製造せず に良品だけを製造するべきであり,筆者らは付加的なコ ストをかけずに製造現場の源流で品質を作り込むことを

(注)品質管理では,サンプリング頻度を検査特性曲線(OC曲線:Operating Characteristic Curve)にしたがって決める。

目指している。その取り組みの一環として、シリコン半導体デバイス(以下、シリコンを省略し、半導体デバイスと記す)の製造工程において製造装置のデータからウェハの加工特性を予測し、仮想的な全数計測が可能となる技術を実用化した。この仮想的な計測技術をヴァーチャルメトロロジー(Virtual Metrologyの略で、以下VMと記す)技術と呼んでいる<sup>1)</sup>。

さらに、VMの結果を製造装置の制御変数(主にプロセス時間)に反映(フィードバック)することによって、工程ばらつきを小さくすることができる。このVMを、もう一歩進化させた技術をVM-APC(VM-Advanced Process Control)と呼んでいる。筆者らは、VM技術を核に、コストと品質を両立させた理想的な半導体デバイスの製造技術の実現に向けて取り組んでいる。

本論文は、半導体デバイスの製造工程の内、最も重要なトランジスタ形成工程におけるVMの実用化の事例について述べる。具体的には、減圧CVD(Chemical Vapor Deposition)装置の成膜速度とそれによる加工寸法ばらつきの低減とトランジスタ特性の予測について、データを交えて述べることによって本論文のコンセプトが半導体デバイスの製造現場で実現可能であることを示す。

# 2. 装置モニタリング技術の構築

VMは装置内で処理されたプロセス結果を装置データから予測する技術であり,装置データを収集することが基本になる。本章では,最初に装置データの収集方法と処理方法について述べる。

#### 2.1 装置データ収集システムの構築

半導体の製造装置には、洗浄装置、成膜装置、露光装置、エッチング装置などがあり、ウェハを一枚ごとに処理する枚葉装置と複数のウェハ(ロット単位)を一括処理するバッチ装置に大別される。そして、これらの製造装置の種類は35種類以上になり、製造装置のベンダーは数十社ある。また、一工程での装置データの種類(装置変数)は数百から数千種類にのぼる。

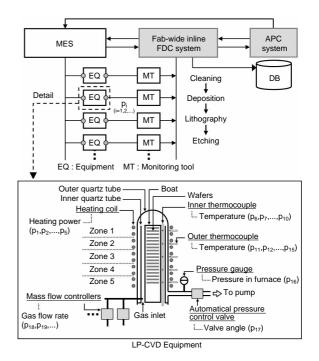

装置データは次のような2つの方法で収集した。1つは, 装置データ収集用のモニタリングツール (MT)を装置 (EQ)の制御コンピュータに接続して,TCP/IP (Transmission Control Protocol/Internet Protocol) 通信を用 いて圧力計や電源などの制御機器における装置変数のデ ータを時間に対するデジタルデータ(トレースデータ)と して収集する。なお、トレースデータのサンプリングレ ートは1 Hzから10 Hzである。もう1つは, MTと計測機器 もしくはセンサを信号線で直接結線し、アナログ信号と して収集する方法である。このアナログ信号を10 Hzで サンプリングすることによってデジタル化し,前述のト レースデータと合せてデータベース(DB)に記録する。 このようにして複数台数と種類の装置からのモニタリン グデータを収集し、そのデータ構造を同一にしてデータ を一元的に扱えるようにする。データの一元化によって, 後述するVMやVM-APCにおいて,装置データの活用度を 飛躍的に向上させることができた(第1図)。実際のとこ ろ,工場レベル(Fab-wide)で形式の異なる装置データを 一元的に収集および処理できる半導体メーカーは少なく、 業界でもトップレベルでデータ収集システムを確立でき たと考えている<sup>2)</sup>。

装置データは、装置やプロセスの異常検知と装置の修繕に用いられる。これをFDC(Fault Detection and Classification)と呼んでおり、非常に重要である。FDCの課題は、装置やプロセスの正常異常をどのように判断するかである。正常異常の判別のために多くの統計的手法が提案されているが、統計的手法だけで装置の正常異常から製品の正常異常を判定することは難しい。それは、製品の製造余裕度が製品ごとに異なるために、装置の正常異常と製品の正常異常が乖離(かいり)するからである。一方、本論文の主題であるVMは、製品における特性の計測結果を

APC : Advanced Process Control LP-CVD : Low Pressure Chemical Vapor Deposition MES : Manufacturing Execution System

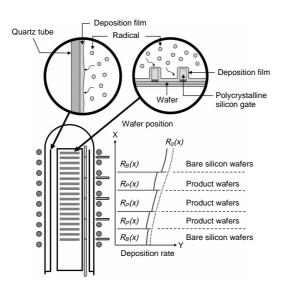

#### 第1図 データ収集システムと減圧CVD装置の概略図

Fig. 1 Schematic drawing of equipment data collection system and equipment for chemical vapor deposition using low pressure

装置データから予測する技術であり、VMが異常であれば 製品が異常であるということを意味する。このことから, FDCにおける正常異常の判定においてもVMは非常に効果 的に機能する(これを筆者らは,VM-FDCと呼んでいる) 次に,具体的な装置モニタリングの事例として,減圧 CVD装置の結果について述べる。

#### 2.2 減圧CVD装置のモニタリング

第1図は、トランジスタ形成工程で用いられるシリコン酸化膜の減圧CVD法を用いた堆積装置と装置データ収集システムの概略図である。

シリコン酸化膜を成膜するために,ウェハを充填したボートが石英製の炉の中に装填される。炉内の温度は5ジーンに分割配置した抵抗加熱式ヒータと複数の熱電対によって制御されている。そして,温度を約740 に制御した状態で炉内にSiH<sub>2</sub>Cl<sub>2</sub>ガスなどの材料ガスを流し,ウェハ上にシリコン酸化膜を成膜する<sup>3)</sup>。

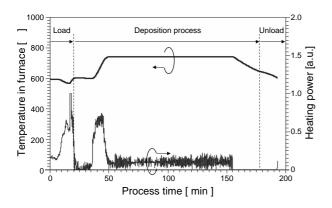

減圧CVD装置で収集した装置変数は,熱電対温度,ヒータ電力,炉内圧力やガス流量などである。第2図は,ヒータ電力と炉内温度のモニタリング結果の一例である。ボート装填(Load)時にヒータ電力が時間に対して複雑に変化しているが,これは炉内の温度を一定にするためであることがわかる。このように装置データの変化には意

第2図 ヒータ電力と炉内温度のモニタリング結果

Fig. 2 Profile of heating power and temperature in furnace collected by monitoring tool

味があり、装置の動作や状態変動が如実に現れる場合が 多い。したがって、装置データを解析することによって、 装置とプロセスの挙動を理解することが可能となる。

# 3. ヴァーチャルメトロロジー

半導体デバイス製造の場合,ウェハプロセスでの加工寸法,エッチング量,成膜の膜厚などがインライン計測している物理量であり,それらがVMの対象になる。筆者らが既に開発および実用化しているVMは,プラズマエッチング装置のパーティクル数やエッチング速度,成膜装置の成膜速度,CMP(Chemical Mechanical Polishing)装置の研磨速度,めっき装置のめっき液の劣化度などである1).4)。

枚葉装置ではウェハごとに装置データを収集しており, ウェハ上のプロセス結果は比較的予測しやすい。しかし, 本論文で述べる減圧CVD装置は,複数のウェハを一括処 理するバッチ装置であり,各ウェハ上の成膜量を高い精 度で予測することは難しい。

#### 3.1 ヴァーチャルメトロロジー技術の概要

VMを開発するためには、まず装置変数のトレースデータから平均値や標準偏差などのサマリーデータを求める必要がある。ここで重要なことはトレースデータをサマリーデータで表現しきることである。したがって、1回のプロセスで収集したトレースデータから多くのサマリーデータを生成する。場合によっては、単純な統計量だけでなくトレースデータを周波数解析したデータなどを求めることがある。サマリーデータを用いてインライン計測で得られる物理量を予測するためには、VMモデル式が必要である。

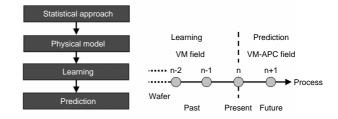

次に, VMモデル式の開発の流れについて述べる(第3

第3図 VMモデル式の開発フローとVM検証の概念図 Fig. 3 VM development flow and concept of its validation

図)。サマリーデータに変換した後は,まず統計的な手法を用いて予測対象の物理量に対して寄与度の高い装置変数を求める。具体的には,主成分分析の1つであるPLS(Partial Least Squares or Projection to Latent Structures)法<sup>5)</sup>や回帰2木決定法<sup>6)</sup>を用いて装置変数の寄与度を算出する。そして,統計的な手法で求めた装置変数を用いて物理モデルを構築し,VMモデル式を決定する。

ここで、VMモデル式の開発および検証の概念について述べる(第3図)。製造装置における現在のプロセスをn回目とすると、n-1回目以前の過去に終了したプロセスで収集された装置データを使用してVMモデル式を求める。VMモデル式は重回帰式がもっとも簡便であるが、エッチング速度などではレート方程式を想定したモデル式も用いられる。これも予測と考えられなくはないが、筆者らはVMモデル式の学習(フィッティング)と呼んでいる。

したがって、本論文における予測は、VMモデル式を固定しておいて現在のプロセスより先のn+1回目以降のプロセスに対するものを指している。VMを実現するだけならばモデルの学習だけでよいが、インライン計測の削減やVM-APCを実現するためには予測が必須になる。

### 3.2 減圧CVD装置における成膜速度の予測

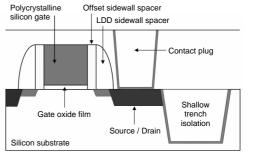

本論文において, VMを実証する対象とした半導体デバイスのトランジスタ断面構造の概略図を示す(第4図)。

LDD : Lightly Doped Drain

第4図 トランジスタの断面構造の概略図

Fig. 4 Cross-sectional view of switching transistor

多結晶シリコンで形成したゲート電極の側壁部分に,膜厚10 nm程度のシリコン酸化膜のオフセットサイドウォールを形成する。この膜厚は,トランジスタの閾値電圧や飽和電流といった電気特性に大きな影響を与えることが知られている。減圧CVD装置の成膜速度を予測するために,装置変数およびデバイス情報を含めた82個の変数から成膜速度に影響度の大きい変数をPLS法によって求める。PLS法で求めた成膜速度に対する寄与度は,1回のプロセスで処理するウェハ枚数,ゲート周囲長およびヒータ電力の順に大きく,これらの変数が成膜速度に影響が大きいことがわかった。次に,寄与度の大きい変数を中心に成膜速度の物理モデルについて述べる(第5図)。

バッチ型の減圧CVD装置では,製品ウェハ上とベアシリコンウェハ(炉の上下部に装填)上の両方にシリコン酸化膜が成長する。製品ウェハでは,パターンの凹凸のために実質的な表面積はベアシリコンウェハより広いので,炉内位置xに対して製品ウェハ上の成膜速度 $R_P(x)$ はベアシリコン上の成膜速度 $R_B(x)$ と異なる。また,炉内の温度分布は均一に制御するが,ガス供給系や排気系のような装置の非対称性のために成膜速度は炉内の位置によっても異なる。成膜速度の炉内位置x0依存性を考慮すると,x0次の体系。

第5図 成膜速度変化のメカニズムを示す模式図 Fig. 5 Physical model in deposition rate behavior

また,プロセス回数が増加していくと,炉の内壁に堆積した膜が厚くなるためにヒータからウェハへの熱伝導度が低下する。その結果,成膜速度は低下することになる。しかしながら,供給律速を仮定すると供給した成膜種(ラジカル)は製品とベアシリコンウェハ上もしくは

炉の壁面上のいずれかで消費されることになる。したがって,筆者らはI回の成膜プロセスにおける成膜量 $D_T$ は(1)式で表現できると考えた。

ここで, $D_P$ は製品ウェハ上の成膜量, $D_B$ はベアシリコンウェハ上の成膜量, $D_0$ はウェハ以外の壁面上の成膜量を示している。

さらに,プロセス制御を行うためには成膜量から成膜速度を算出しておく方が都合が良いので,成膜速度 $R_p(x)$ を以下の(2)式から求めることを考案した。第1項の総和はゲート周囲長などのデバイス情報から求まる要素で,第2項の総和と第3項の $R_0$ が装置変数から求まる要素を示している。

ここで, $A_i$ と $B_i$ は係数, $L_i$ はデバイス情報, $n_i$ は製品枚数, $P_i$ は位置情報である。さらに, $R_0$ はヒータ電力などの装置変数 $P_i$ の(i=1から4)重回帰式で下記のように求める。

$$R_{\theta}(x) = a_{\theta} + \sum_{i=1}^{4} a_{i} p_{i} \cdots (3)$$

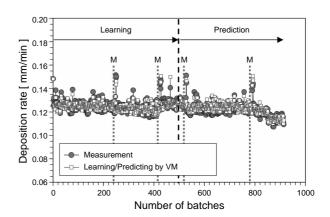

ここで, $a_0$ , $a_i$ は回帰係数である。以上の(2)式と(3)式を用いて求めた成膜速度のVMと実際の成膜速度の測定結果を,**第6図**に示す。なお,**第6図**中のMは装置のメンテナンス(石英炉やウェハ支持ボートの交換など)を示している。

第6図 成膜速度の測定結果とVMによる学習結果および予測結果の 比較

Fig. 6 Comparison in deposition rate among measurement, learning and prediction by VM

成膜速度の実測値とVMモデル式の学習による計算値および予測値との相関係数は,それぞれ0.90と0.94であり,ほぼ完全に成膜速度を予測できていることがわかる。こ

こで注目すべきことは、装置のメンテナンスが行われてもVMモデル式を再学習させることなく、成膜速度を予測できていることである。このことは、筆者らが考案したVMの開発手法が有効であることを示している。

# 4. ヴァーチャルメトロロジーとプロセス制御

# 4.1 新しいプロセス制御技術 (VM-APC)

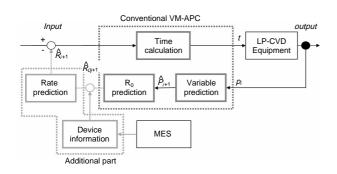

第3章で述べたように,成膜速度をVMによって高精度に予測することができると,その結果を用いたVM-APCが可能となる。従来のプロセス制御では定点管理した成膜速度の実測結果をフィードバックし,目標の膜厚になるように算出した時間を装置に人手で入力していた。

VMを用いた自動制御を製造現場で実用化するためには、製造実行システム(MES: Manufacturing Execution System) および製造装置と連携した専用のシステムが必要である。VM-APC専用のシステムは、製造品種やプロセスレシピの変更などと連動する要素が非常に多く、複雑なシステムなので開発が難しい。筆者らは、CMP装置などでVM-APC技術を既に実用化していたのでVM-APCシステムを構築済みであった。そのため、オフセットサイドウォール膜厚のVM-APCを構築済みのシステムに若干の修正を加えるだけで実現できた(第7図)。

第7図 VM-APCによる膜厚制御アルゴリズム Fig. 7 Control algorithm of thickness by VM-APC

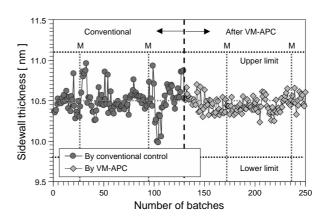

#### 4.2 高精度膜厚制御によるばらつき低減

第8図に、VM-APCによるゲート電極のオフセットサイドウォール膜厚と人手による制御結果を示す。従来の人手による制御では工程能力指数Cpk <sup>7)</sup> は1.18であり、1.33を満足していないが、VM-APCによってCpkは2.23まで向上していることがわかる。従来の制御では、インライン計測後からプロセス時間を変更するまででタイムラグが起こってしまう。このタイムラグの間に吸収しきれない装置変動が発生するため、膜厚ばらつきが大きくなったと考えている。なお、今回のVM-APC技術を同じ型式の

第8図 従来制御とVM-APCによるオフセットサイド ウォール膜厚の比較

Fig. 8 Comparison of offset sidewall thickness controlled by conventional control and by VM-APC

装置3台に導入したが、Cpkはすべて2を超えていることを確認している。

# 5. 新しい半導体デバイス製造技術

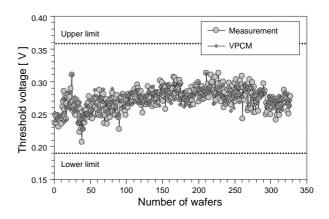

VM技術の到達地点は、製品の電気特性を工程内で予測するということである。筆者らは、これをVPCM(Virtual Process Control Module)と呼んでいる。その一例として、トランジスタの閾値電圧の実測値とVPCMによる予測した結果について述べる(第9図)。

トランジスタの閾値電圧を,オフセットサイドウォール膜厚,ゲート酸化膜厚やゲート電極寸法などのデータを用いて予測した。実測値と予測値の相関係数は0.8で非常に良好であることがわかる。従来,製品の電気特性はすべてのデバイス製造工程が終了した後で測定するので,

第9図 トランジスタ閾値電圧の実測値とVPCMによる計算結果の比較 Fig. 9 Comparison of threshold voltage in transistor measured by PCM and calculated by VPCM

このように工程の途中で特性を予測できることは,歩留まりの維持に非常に効果的である。

ここまで述べてきたVM-APCやVPCMを核とするVM技術の効果には、製造ばらつきの低減以外にもうIつメリットがある。それは、インライン計測をせずに(測らずに)品質を向上させる理想的なモノづくりを実現できることである。従来、半導体デバイスの製造では、微細化とウェハの大口径化による生産性の向上によって製造コストを低減してきた。VMに関連する技術を活用すれば、計測費用の最適化と品質向上によって製造コストを削減することができる。

# 6. **まとめ**

半導体デバイス製造における製造装置のモニタリング 技術について筆者らが取り組んできた内容を簡単に説明 し、VM技術の考え方を含め概要を述べた。

VM技術の具体的な事例として,トランジスタ形成工程におけるゲート電極のオフセットサイドウォール膜厚を制御するために,減圧CVD装置のデータを用いて成膜速度を予測するVMモデルを開発した。この成膜速度のVMモデルによる実測値と学習値および予測値との相関係数は0.90と0.94であり,非常に良好であることを示した。

さらに、VMによる成膜速度の予測値を用いたVM-APCによってオフセットサイドウォール膜厚のばらつきを低減し、膜厚のCpk を2.23まで向上させることができた。

最後に、トランジスタの閾値電圧を予測するVPCMについて述べ、閾値電圧の実測値と予測値の相関係数が0.8であることを示した。トランジスタの閾値電圧は一般的に半導体デバイスの製造が完了した後に測定するものであり、製造工程の途中で予測できる意義は非常に大きい。

以上述べてきたように,ナノスケールの半導体デバイスにおいて製造難易度が向上している中で,抜き取りによるインライン計測や製品完成後の検査を中心とした品質確保や歩留まり向上には限界がある。したがって,本論文で筆者らが示した製造形態がモノづくりの究極の姿の1つであると予想している。

筆者らは、製造装置のデータを核にVMやVPCMを用いた革新的な半導体デバイスの製造技術を製造現場で実用化するとともに、それを進化させた究極のモノづくりを目指し、お客様によりよい製品をお届けすべく日々の研鑽に努めている次第である。

#### 参考文献

- S. Imai: Virtual metrology for plasma particle in plasma etching equipment. International Symposium on Semiconductor Manufacturing 2007, CA, pp.346-349 (2007).

- 2 ) S. Imai, et al.: Fab-wide equipment monitoring and FDC system. International Symposium on Semiconductor Manufacturing 2006, Tokyo, pp.114-117 (2006).

- 3 ) E. Dehan, et al. : Semi-insulating polycrystalline silicon by low pressure chemical vapour deposition from disilane and nitrous oxide. Jpn. J. Appl. Phys. 34,pp.4666-4672 (1995).

- 4 ) S. Imai et al. : Prevention of copper interconnection failure in system on chip using virtual metrology. IEEE Transaction on Semiconductor Manufacturing (to be submitted).

- 5) S. Wold, et al.: PLS-regression: a basic tool of chemometrics. Chemometrics and Intelligent Laboratory Systems 58,pp.109-130 (2001).

- 6 ) L. Breiman, et al.: Classification and Regression Trees (Chapman & Hall) p.10 (1984).

- For example, S. Kotz et al.: Process Capability Indices (Chapman & Hall) p.51 (1993).

#### 著者紹介

今井伸一 Shin-ichi Imai 先行デバイス開発センター Advanced Devices Development Center 博士(工学)

安田 哲 Satoshi Yasuda セミコンダクター社 生産本部 Corporate Manufacturing Div., Semiconductor Company