# パルスレーザー堆積法によるガラス基板上 ZnO-TFT の作製と特性評価\*

吉田 太一・橘 達也・前元 利彦・佐々 誠彦・井上 正崇 工学研究科 電気電子工学専攻 (2009 年 9 月 30 日受理)

Characterization of ZnO thin-film transistors fabricated by pulsed laser deposition on glass substrates by

Taichi YOSHIDA, Tatsuya TACHIBANA, Toshihiko MAEMOTO, Shigehiko SASA, Masataka INOUE

Major in Electrical and Electronic Systems Engineering, Graduate School of Engineering (Manuscript received September 30, 2009)

Memoirs of the Osaka Institute of Technology, Series A Vol. 54, No. 2(2009) pp. 9~15

# パルスレーザー堆積法によるガラス基板上 ZnO-TFT の作製と特性評価\*

吉田 太一\*\*・橘 達也\*\*・前元 利彦・佐々 誠彦・井上 正崇 工学研究科 電気電子工学専攻 (2009年9月30日受理)

Characterization of ZnO thin-film transistors fabricated by pulsed laser deposition on glass substrates by

Taichi YOSHIDA, Tatsuya TACHIBANA, Toshihiko MAEMOTO, Shigehiko SASA, Masataka INOUE

Major in Electrical and Electronic Systems Engineering, Graduate School of Engineering (Manuscript received September 30, 2009)

#### **Abstract**

We report the characterization of zinc oxide (ZnO) thin-film transistors (TFTs) on a glass substrate fabricated by pulsed laser deposition (PLD). ZnO films were characterized by X-ray diffraction (XRD), atomic force microscope (AFM) and Hall effects measurement. The XRD results showed high c-axis oriented ZnO (0002) diffraction corresponding to the wurtzite-phase. Moreover, the crystallization and the electrical property of ZnO thin films grown at room temperature are controllable by PLD growth conditions such as oxygen gas pressure. The surface roughness of the ZnO films is very smooth, with a root-mean-square roughness of 1 nm. The Hall effect measurements show that we have succeeded in fabricating a ZnO film on glass substrates with an electron mobility of 21.7 cm $^2$ /Vs. By using a ZnO thin film grown at room temperature and a HfO $_2$  gate insulator, a transconductance of 24.5 mS/mm, drain current on/off ratio of 4.4 × 10 $^6$ , and subthreshold gate swing of 0.26 V/decade were obtained.

キーワード; 酸化亜鉛,パルスレーザー堆積法,薄膜トランジスタ,ガラス基板

**Keyword**: Zinc oxide (ZnO), Pulsed Laser Deposition (PLD), Thin film transistor (TFT), Glass substrate

- \* 2009年応用物理学会学術講演会にて口頭発表(2009年3月31日, 筑波大学)

- \*\* 大阪工業大学大学院工学研究科電気電子工学専攻

### 1. 研究背景と目的

今日, 薄くて軽くて綺麗な平面ディスプレイ(flatpanel display, FPD) が携帯電話, PC, テレビなどに使 われることによって私たちの生活を豊かにまた便利 にしている. このようなFPDの駆動素子として使 われる半導体デバイスはコストと利用可能な基板の 制約によりプロセス温度が250℃以下で実現される 必要がある. そのため、現在、FPDには大面積均 一成膜特性, 再現性, 安定性, 安全性, 微細加工特 性と言った半導体プロセスに対する優れた特性を持 ち, 低温成膜可能な水素化アモルファスシリコン (a) -Si:H) が主に使用されている. しかしa-Si:Hには 移動度が低いという欠点がありこれはFPDの大面 積化や有機ELに代表される電流駆動型のデバイス の駆動素子にa-Siを使うには特性の改善が求められ ている。また最近はフレキシブルエレクトロニクス のFPDへの応用が期待されており、プロセス温度 に制約のあるプラスチック基板上へ半導体デバイス を作製することが必要となる. 低温成膜したSiを用 いたデバイスとしては、a-Siをレーザーアニールす ることにより基板温度を上げることなく得られる多 結晶シリコン (poly-Si) のFPDへの応用が盛んに 研究されている<sup>1,2)</sup>. poly-Siはa-Siに比べ移動度が 2桁ほど高いため電流駆動性能が大きいという特徴 があるが、均一性が低く、有機ELディスプレイに 使用するには特性のばらつきを補償する回路が必要 であり、これはディスプレイの開口率を下げるとい う問題もある.

そこで近年、Siに続く新しい低温大面積用デバイスとして酸化物半導体を用いたデバイスが盛んに研究されている。これは酸化物半導体が実用化されているSiと比べバンドギャップが大きく透明であることや、低温成膜しても移動度が高いという特徴を持っているため、透明導電性酸化物(TCO)と組み合わせることにより完全に透明なデバイスへの開発が志向されているからである。その中でもアモルファス酸化物半導体(Amorphous oxide

semiconductor, AOS)は2004年に東工大の野村らによって $\alpha$ -InGaZnO( $\alpha$ -IGZO)を活性層に用いたポリエチレンテラフレート基板上薄膜トランジスタ(Thin-filmtransistor, TFT) $^{3}$ )が報告されて以来,注目を浴び多くの研究機関で研究されており, $\alpha$ -IGZOを用いた有機ELディスプレイも実証 $^{4}$ )されている。しかし、IGZOには資源の枯渇化が問題とされているレアメタルであるInが使われており,これはデバイスのコストや環境面でも問題となる.

そこで我々は酸化物半導体として生態系への親和 性, 環境適合性に優れた酸化亜鉛(ZnO)に注目し た. ZnOはこれまで化粧品, 顔料, 陶磁器として使 用されてきたように人体に無害な材料である. ま たZnOのバンドギャップは3.37 eVでAOSと同様に ZnOを活性層に用いたTFTは多くの研究機関で研 究されてきた<sup>5,6)</sup>. 本学ナノ材料マイクロデバイス 研究センターにおいても、これまでに分子線エピ タキシー (Molecular beam epitaxy, MBE) 法を 用いて、サファイア基板上にZnO/ZnMgOへテロ 構造を作製することにより2次元電子ガス (Two dimensional electrongas, 2DEG) 層を形成し, これを活性層に取り入れたヘテロ接合MIS型電界 効果トランジスタ (Hetero-MIS-FET) 7.8) やこ のFETを用いた生態適合性の高いバイオセンサー9) について報告してきた.

本研究ではパルスレーザー堆積(pulsed laser deposition, PLD)法を用いて汎用性の高いガラス基板上に加熱成膜されたZnO薄膜を活性層に利用したTFTを作製、諸特性の評価を行うことにより、TFT作製プロセスの確立を目指した。またフレキシブル基板への応用も念頭におき、室温成膜されたZnO薄膜を用いてTFTの作製および評価を行った。

#### 2. 加熱成膜したZnOを用いたTFTの作製と特性評価

# 2.1 単層ZnO膜のPLD成長

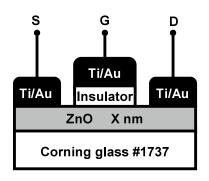

Fig. 1 に試料構造を示す. PLD法によりZnO薄膜をCorning #1737ガラス基板上に成膜した. ZnOの

Fig. 1 Schematic of the fabricated ZnO TFT.

アブレーションにはNd:YAGレーザーの第四高調波 266 nm,繰り返し周波数10 Hzを使用した.成膜条件としてターゲット – 基板間距離を $40\,\mathrm{mm}$ ,基板温度を $360\,^{\circ}\mathrm{C}$ と一定にした.成長中の酸素分圧を $1\times10^{-5}\sim10^{-3}$  Torrの範囲で変化させ,膜厚についてはTFTを作製するため $100\,\mathrm{nm}$ , $50\,\mathrm{nm}$ とした.X線回折測定(XRD),原子間力顕微鏡(AFM),ホール効果測定によって薄膜の諸特性を評価した.またフォトリソグラフィ技術とウェットエッチングを用いてゲート幅 $W_g=50\,\mu\mathrm{m}$ ,ゲート長 $L_g=1\sim50\,\mu\mathrm{m}$ のトップゲート型TFTを作製した.オーミック,ゲート電極には $\mathrm{Ti}/\mathrm{Au}$ ,ゲート絶縁膜には膜厚  $100\,\mathrm{nm}$ の $\mathrm{SiO}_2$ を用い、それぞれ電子ビーム蒸着装置を用いて蒸着した.

諸特性を評価しながら酸素分圧と膜厚の最適化を行った. ZnOの膜厚をX=100 nmと一定とし、酸素分圧を変化させた試料でTFTを作製したところ、酸素分圧1×10<sup>-5</sup> Torrで成膜したTFTではドレイン電流の変調が見られず、1×10<sup>-3</sup> Torrで成膜したTFTでは電子移動度、電子濃度が低下したためON電流の減少が見られた. 一方、酸素分圧1×10<sup>-4</sup> Torrで作製したTFTでは明瞭な電流変調が見られたもののON/OFF比が3.6とTFTとして十分なOFF特性が得られなかった. 以上の結果から、活性層の膜厚が厚いことが原因で活性層の十分な空乏化が得られなかったためON/OFF比が低くなったと考え、ZnOの膜厚を50 nm、成膜中の酸素分圧を1×10<sup>-4</sup> TorrとしてTFTを作製し活性層の膜厚の最適化を行った.

#### 2.2 単層ZnO薄膜の特性評価

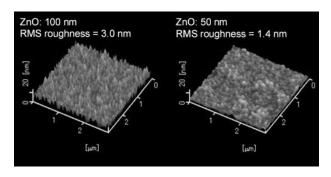

Fig. 2 に作製したZnO薄膜のAFMによる表面モホロジーを示す. 薄膜の膜厚はそれぞれ100 nmと50 nmである. 50 nmの薄膜のRMS粗さは1.4 nmで100 nmの薄膜よりも平坦であることが分った. 実験結果は、1 nm程度のRMS粗さを持つガラス基板の平坦性を反映し、より薄い膜が平坦でTFT構造の作製に有利であることをが分かった.

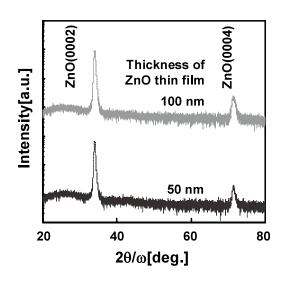

Fig. 3 にXRDスペクトルを示す。 ZnO(0002) 面からの回折ピークが観測され、他の結晶面からの回折ピークが観測されていないことから、膜厚によらずZnO薄膜がc軸配向していることが分った。 Table. 1 にはホール効果測定により求めた電気的特性をまとめた.

Fig. 2 AFM morphology of the ZnO films surface.

Fig. 3 XRD spectra for ZnO thin films.

Table. 1 Electrical properties of ZnO films

| Thickness (nm) | Mobility (cm <sup>2</sup> /Vs) | Carrier density<br>(cm <sup>-3</sup> ) | Sheet resistance $(k\Omega/cm^2)$ |

|----------------|--------------------------------|----------------------------------------|-----------------------------------|

| 100            | 31.0                           | $1.64 \times 10^{19}$                  | 1.2                               |

| 50             | 36.8                           | $7.22\times10^{18}$                    | 4.7                               |

## 2.3 ZnO-TFTの特性評価

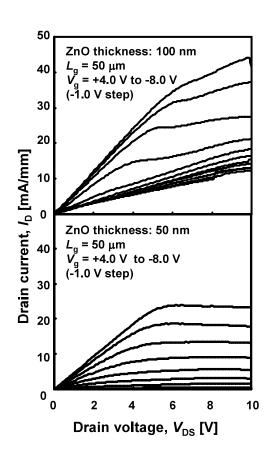

Fig. 4 にゲート長が $50 \mu m o ZnO$ -TFTの出力特性を示す。ZnOo 膜厚が100 nmo TFTでは変調が見られるものの,電流のOFF特性が見られなかった.一方,膜厚が50 nmo TFTではドレイン電圧 $V_{DS}$  が低いときにはドレイン電流 $I_D$  が比例して増加し,高い $V_{DS}$  では飽和する,ピンチオフ特性と明瞭なOFF特性を示した.またゲート電圧 $V_{CS}$  が 0 Vのとき,ドレイン電流 $I_D$  はOFFせず流れているためこのTFTはディプレッションモードで動作している

Fig. 4 Output characteristics of ZnO-TFTs.

Fig. 5 Transfer characteristics of ZnO-TFTs.

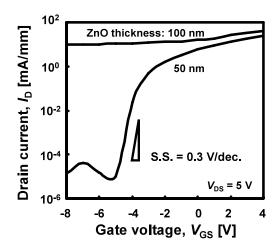

ことが分った。Fig. 5 には $V_{DS}$  = 5 Vでの伝達特性を示す。ZnOの膜厚を薄くすることによってOFF特性の大幅な改善が確認できた。ZnOの膜厚が50 nmのとき最大相互コンダクタンス, $g_{m}$  = 5.4 mS/mm,ON/OFF比 =  $1.3 \times 10^{6}$ ,サブスレッショルドスイング,S.S. = 0.3 V/dec.,しきい値, $V_{TH}$  = -3.9 Vが得られた.

# 3. 非加熱でPLD成長したZnO薄膜を用いた TFTの作製と特性評価

### 3.1 非加熱ZnO 薄膜の特性評価

前節では加熱成膜したZnOを活性層に用いた TFTを作製し、TFT作製プロセスの確立を行った. 本節では、プラスチックなどの耐熱性の無い基板上 にTFTを実現できるプロセスを確立するため、非 加熱でのZnO薄膜のPLD成長およびTFTの特性に ついて述べる.

基板にはCorning#1737を用いた。酸素分圧  $1 \times 10^4$  Torrで非加熱成膜した膜厚が $50 \, nm$ のZnOを用いて TFTを作製したところ、ピンチオフ特性は観測できたが十分なOFF特性が得られなかった。室温成膜でのZnO薄膜の結晶性が悪く、構造欠陥に起因する電子濃度増大のため活性層の十分な空乏化が起こらず十分なOFF特性が得られなかったと考えられる。そこで成長中の酸素分圧を  $1 \times 10^{-3} \sim 10^{-2}$  Torr

と変化させ、膜厚をさらに薄く $40\,\mathrm{nm}$ として $\mathrm{ZnO}$ 薄膜を成膜した。酸素分圧  $1\times10^{-3}\,\mathrm{Torr}$ で成膜した場合、 $10^{19}\mathrm{cm}^{-3}\,\mathrm{on}$ 高電子濃度となったが、 $1\times10^{-2}\,\mathrm{Torr}$  の場合、 $7.7\times10^{17}\mathrm{cm}^{-3}\,\mathrm{と電子濃度}$ が一桁以上低い $\mathrm{ZnO}$ 薄膜が得られた。この $\mathrm{ZnO}$ 薄膜を活性層に用いて $\mathrm{TFT}$ を作製したところ、電子濃度の低下により $\mathrm{ON}$ 電流も減少し相互コンダクタン $\mathrm{Zg_m}$ が低下した。

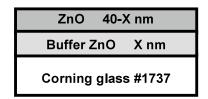

先に述べた高酸素分圧での実験結果を参考に、Fig.6に示す様な試料構造を検討した。 $1\times10^{-2}$  Torrの高酸素分圧で成膜したZnO薄膜をバッファ層に用い、その上に $1\times10^{-4}$  Torrで成膜したZnO 層を活性層とした構造を作製した。このとき全体の膜厚を $40\,nm$ と一定にし、薄膜の特性評価およびTFTの作製と評価を行った。また更なる特性の改善のためゲート絶縁膜としてHigh-k材料である $HfO_2$ を用いた。 $HfO_2$ の膜厚は $100\,nm$ とした。

Fig. 6 Schematic of a sample structure. First, a thin ZnO buffer layer was deposited at room temperature in  $1 \times 10^{-2}$  Torr of oxygen. Next, the undoped ZnO channel layer was deposited in at room temperature  $1 \times 10^{-4}$  Torr. The total thickness of films was in the range of 40 nm.

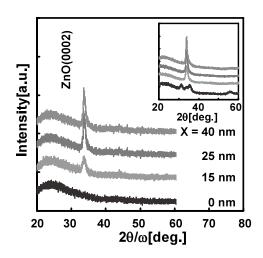

作製した薄膜のXRDスペクトルをFig.7に示す.バッファ層の膜厚が0 nm, つまり膜全体を $1 \times 10^{-4}$  Torrで成膜したZnO薄膜からは回折ピークが観測されなかった. 差し込み図に示した微小角度入射法(入射角 $0.5^\circ$ ) で測定したスペクトルからは多数の回折ピークが観測でき、薄膜中にさまざまな方位の結晶が存在していることが分かった. 一方、バッファ層の膜厚が40 nm, つまり膜全体を $1 \times 10^{-2}$  Torrで成膜したZnO 薄膜のスペクトルではZnO (0002) 面からの回折ピークが観測され酸素分圧を高くすることで

Fig. 7 XRD spectra of ZnO thin film with buffer layer.

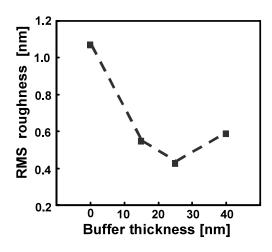

Fig. 8 RMS roughness of ZnO films with buffer layer.

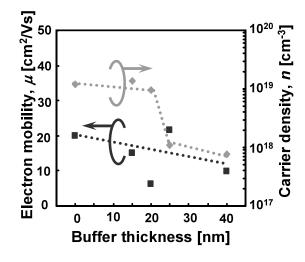

Fig. 9 Electron mobility and carrier density of ZnO thin films with buffer layer.

ZnO薄膜がc軸配向することが分った. これは高酸素分圧にすることでZnOの成膜条件がストイキメトリーに近づいたためと考えられる. 一方, バッファ層を挿入した構造でのスペクトルでもZnO (0002) 面からの回折ピークが観測され, バッファ層の膜厚が増加すると回折ピーク強度が増加して結晶性が改善できることが分かった.

Fig. 8 にAFMにより求めたそれぞれの構造についてRMS粗さを示す. バッファ層を挿入することでZnO薄膜がc軸に配向したことから表面粗さも改善されたと考えられる. バッファ層を挿入したときのRMS粗さは $0.6\,\mathrm{nm}$ 以下でより平坦な薄膜が得られた. Fig. 9 に各々の構造でのホール効果測定の結果を示す.  $25\,\mathrm{nm}$ 以上のバッファ層を挿入することで電子濃度が低減され, バッファ層の膜厚が $25\,\mathrm{nm}$ のとき電子濃度 $1.1\times10^{18}\,\mathrm{cm}^{-3}$ , 電子移動度 $21.7\,\mathrm{cm}^2/\mathrm{V}$ sが得られた. バッファ層を挿入することで結晶性が改善され, 構造欠陥に起因するキャリアの発生が抑えられたことで電子濃度が減少したと考えられる.

# 3.2 非加熱プロセスZnO-TFTの特性評価

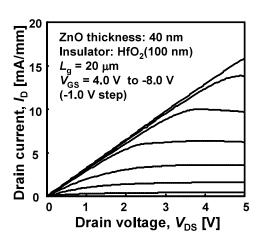

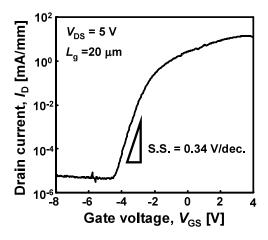

バッファ層の膜厚が $25\,\mathrm{nm}$ の薄膜を用いて作製したゲート長が $20\,\mu\mathrm{m}$ の $Z\mathrm{nO}$ -TFTの出力特性と伝達特性をFig.10およびFig.11に示す. 出力特性より明瞭なピンチオフ特性が見られ、またディプレッションモードで動作していることが分った. このとき、最大伝達コンダクタンス $g_\mathrm{m}$ = $4.2\,\mathrm{mS/mm}$ と求まった. また、伝達特性からON/OFF比= $4.4\times10^6$ 、S.S.= $0.34\,\mathrm{V/dec}$ 、 $V_\mathrm{TH}$ = $-2.9\,\mathrm{V}$ が求まった.

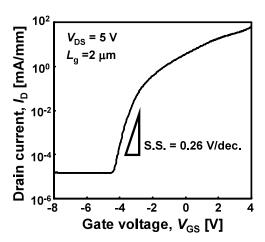

Fig.12にゲート長  $2\mu m$ のTFTの伝達特性について示す。ゲート長を縮小させることで $g_m$ が24.5 mS/mmまで増加し、S.S.が0.26 V/dec.に減少したことから素子の微細化によりTFTの特性が大きく向上した。

Fig. 10 Output characteristic of ZnO TFT with buffer layer.

Fig. 11 Transfer characteristic of ZnO TFT with a  $20-\mu$ m-long gate.

Fig. 12 Transfer characteristic of ZnO TFT with a 2-μm-long gate.

#### まとめ

パルスレーザー堆積 (PLD) 法を用いてガラス基 板上に加熱および非加熱でZnO薄膜を成膜しTFT を作製した. 加熱成膜したZnO薄膜ではc軸配向し たZnO薄膜が得られた. 活性層の膜厚が50 nm, 成 膜時の酸素分圧が 1×10<sup>-4</sup> Torr, 100 nmのSiO<sub>2</sub>を ゲート絶縁膜としたとき、ゲート長50 μmのTFTに おいて明瞭なピンチオフ特性が得られ、最大コン ダクタンス $g_m = 5.4 \text{ mS/mm}$ , ON/OFF比 =  $1.3 \times 10^6$ という値が得られトップゲート型TFTの作製プロ セスが確立できた. 非加熱成膜したZnO薄膜では酸 素分圧が低い場合にはZnO薄膜はc軸配向せず、高 酸素分圧では を軸配向し結晶性が良くなった. 高酸 素分圧で成膜したZnOをバッファ層に用いた構造で ゲート絶縁膜をHigh-k材料であるHfO2としてTFT を作製した. ゲート長2 µmに微細化した結果, 最 大コンダクタンス $g_m$ =24.5 mS/mm, ON/OFF比= 4.4×10<sup>6</sup>, S.S. = 0.26 V/dec.が得られた. 今回作製し たZnO-TFTはディプレッションモードであり、こ の高い相互コンダクタンスを活かしてバイオセン サーなどのセンサーへの応用も可能と考えられる. さらに、FPDの駆動素子としてはゲート電圧が OV で十分なOFF が得られるエンハンスメントモード であることが望ましい. そのため, 今後はしきい値 をプラスへシフトさせZnO-TFTにおいてエンハン スメント型TFTの作製と、プラスチック基板など のフレキシブル基板上でのTFTの動作を目指す予 定である.

#### 参考文献

- 1) T. Sameshima et al., Proc. Mat. Res. Soc. Symp., 71, 435 (1986).

- T. Sameshima, J. Non-Cryst. Solids, 227-230, 1196 (1998).

- 3) K. Nomura, H. Ohta et al., Nature, 432, 488 (2004).

- 4) H.N. Lee, et al., IDW '06, 663 (2006).

- 5) P. F. Carcia et al., Appl. Phys. Lett. 82, 1117 (2003).

- 6) Satoshi Masuda et al., J. Appl. Phys. 93, 1624 (2003).

- 7) K. Koike et al., Jpn. J. Appl. Phys. 44, 3822 (2005).

- 8) S. Sasa et al., Appl. Phys. Lett., 89, 053502 (2006).

- K. Koike et al., Jpn. J. Appl. Phys., 46, L865 (2007).