# 高性能・低消費電力DSPコア: Hi-Perion シリーズ

New High-performance, Low-power DSP Core: Hi-Perion Series

## あらまし

携帯電話のディジタルベースバンド部で用いられる音声コーデックなどのディジタル 信号処理を高性能かつ低消費電力で実現する16ビット固定小数点DSPコア(Hi-Perion)を 紹介する。

Hi-Perionは,最高動作周波数100 MHzと業界トップクラスの性能を達成した。また,消費電力においても,1.8 Vという低電圧動作を可能にすることで,富士通従来品に比べ70%以下に抑えることができた。Hi-Perionを用いれば,次世代移動体通信の重要な技術要素として注目されているCDMA方式やPDCで用いられている複雑かつ高速処理が要求される音声コーデック処理を低消費電力で実現できる。

本稿では、16ビット固定小数点DSPコアの優れたアーキテクチャ、およびDSPを用いたシステム開発に欠かせない開発環境について説明する。

## Abstract

We have developed a new high-performance, low-power, 16-bit fixed point DSP core (Hi-Perion) for such digital signal processing as speech CODEC used in the digital base band of cellular phones. The maximum operating speed of Hi-Perion is 100 MHz. This device can also operate using a power supply of only 1.8 V, and consumes 70 percent less power than our existing products. Consequently, Hi-Perion enables the complex high-speed speech CODEC processing required in PDC and CDMA (which are essential technologies for the next generation of mobile communications) at significantly reduced power consumption.

This paper describes the architecture of the 16-bit fixed point DSP core and the environment required to develop systems that use a DSP core.

糟谷 武(かすや たけし)

1988年日本大学理工学部電子工学科 卒。同年富士通入社。以来ディジタ ルシグナルプロセッサ開発に従事。 第三システムLSI事業部プロセッサ設

# まえがき

近年の携帯電話や電子手帳に代表される携帯端末の普及に伴い、それらの中核を担うLSIには、半導体素子の微細化による高集積化によって実現するシステムLSI化、携帯ということから、長時間連続使用を可能にする低消費電力化が要求されている。また、それら機器の持つ機能をさらに向上させるために、複雑かつ高速処理のディジタル信号技術を導入することにより、LSIに要求される性能も従来の2倍、3倍になってきている。

このような市場要求から,携帯端末に使用されるDSP もまた,さらなる高性能化,低消費電力化の方向に進ん でいる。本稿では,今回開発したHi-Perionのアーキテク チャや開発環境について紹介する。

## Hi-Perion

Hi-Perionの構成

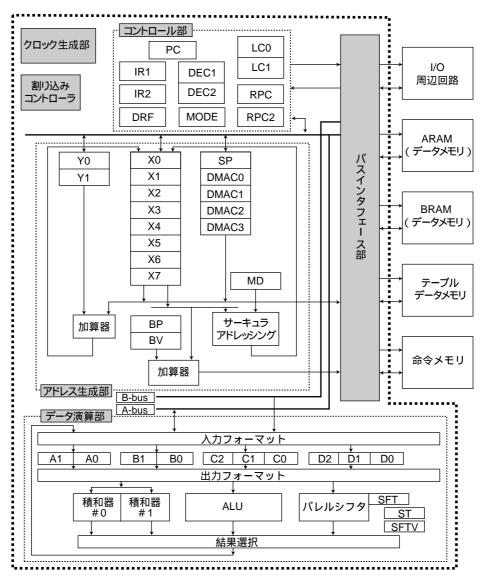

Hi-Perionのブロック図を図-1に示す。本DSPコアは大きく分けて6個のブロックから成る。

## (1) クロック生成部

Hi-Perionの動作に必要なクロックの生成を行う。

#### (2) 割り込みコントローラ

外部要因割り込み(INT割り込み,DMA割り込み,エミュレータからのブレーク割り込み)と内部要因割り込み (オーバフロー割り込み)の受付けおよび許可,プライオリティ制御などを行う。

## (3) コントロール部

プログラムメモリ空間へのアドレス生成を行うプログ

図-1 Hi-Perionプロック図 Fig.1-Hi-Perion block diagram.

ラムカウンタ(PC), プログラムループ機能やリピート機能を制御するループカウンタ(LCO/1), リピートカウンタ(RPC/RPC2), DO制御レジスタ(DRF), 命令フェッチを行うインストラクションレジスタ(IR1/2), フェッチした命令の解析を行うインストラクションデコーダ(DEC1/2)や動作モードを制御するモードレジスタ(MODE)などから成る。

#### (4) アドレス生成部

メモリアクセスに必要なアドレス生成を行う。アドレスレジスタ(X0~X7), アドレス修飾レジスタ(Y0/1), サーキュラアドレッシング機能を実現するためのサーキュラベースポインタ(BV), サーキュラ範囲を示すモジュロレジスタ(MD), その他ベースポインタ(BP), スタックポインタ(SP), DMA転送時に転送先アドレスを示すDMAアクセスポインタ(DMAC0~DMAC3)から成る。

# (5) データ演算部

データレジスタに対して,積和,四則演算,論理演算,シフト演算などのデータ演算を行う。データレジスタ(A0/1,B0/1,C0/1,D0/1)と前記レジスタを統合したアキュムレータ(CX,DX),演算結果や内部状態を示すステータスレジスタ(ST),シフトレジスタ(SFT,SFTV),2組の積和器(MAC),四則演算や論理演算などを行うALU,シフト演算を行うパレルシフタから成る。

## (6) パスインタフェース部

DSPコアと周辺回路のインタフェースを行う。命令空間からの命令の読み出し、データメモリへのアクセス、マップドI/Oアクセスなどメモリ空間に対するウェイト制御を含むアクセス制御を行う。

Hi-Perionの特徴

- (1) 固定小数点演算(ガードビット有/無しモードサポート)

- ・乗算 16ビット × 16ビット 31ビット

- ・加算 40ビット + 40ビット 40ビット

- ・積和演算

40ビット ± 16ビット × 16ビット 40ビット

(2) Dual-MACアーキテクチャ

積和演算は2組の積和演算器(MAC)で交互に動作させることにより実現

(3) インターロック機能

命令の組み合わせにより発生するパイプラインハザー ドを自動的に調整し,ハザードによる命令未実行を防ぐ

- (4) データ丸めおよびクリップ機能

- ・演算結果に対してだけでなく,データ転送時にも働くクリップ機能有り

- ・データ丸め機能はデータ転送のみに有効

- (5) 特徴的な命令

- ・メモリ間転送

- ・条件付き転送

- ・Doループ内で使用できるリピート

- ・加算減算同時実行

- ・特殊比較

- (6) 演算速度

- **処理能力** 最大100 MIPS

- (7) 3種類の動作モードをサポート

- (8) メモリ空間(シングルチップモード時)

最大以下の領域までメモリの配置が可能 ・データRAM ARAM 最大 4 kワード × 16ビット

BRAM **最大** 4 k**ワード** × 16**ビット**

- (9) アドレッシング

- ・二つの独立したアドレスユニット

- ・8本の汎用レジスタ

- ・レジスタの更新機能付アドレッシング

- ・サーキュラアドレッシング

- ・2本のアドレス更新用レジスタ

命令セット

携帯電話の音声コーデック処理に効果的な命令,および従来品になかった新規命令について以下に説明する。

(1) 条件付き転送命令(MVcc)

本命令は,DSPの演算結果(ステータスレジスタのキャリーフラグやゼロフラグなど)によってある条件が成立した場合,転送を行う。本命令を適用することにより,コードブックサーチ処理が従来8サイクルかかっていたものを6サイクルにできた。また,コードブックサーチはループ処理で行うためループ回数をNとすると,トータルで2Nサイクル減の効果がある。

(2) DO**ループ処理内のリピート命令(**REP2)

本命令は、2重ループを必要とする演算に効果を発揮する。本命令を適用することにより、自己相関処理を従来 $\{92 + 11 \times (N - k)\}$ サイクルかかっていたものを $\{77 + 11 \times (N - k)\}$ サイクル $\}$ にできた。

(3) メモリ間転送(MOV memory to memory)

メモリ間転送は,あるメモリバンク(ARAM)から別の メモリバンク(BRAM)へダイレクトに転送する機能であ る。同じような処理は,本DSPのストアロード命令 (STLD)で実現できるが,この場合,レジスタを介した転

| コードブックサーチ(従来品) |                    |                                                            |                                                 | コードブックサーチ(Hi-Perion) |                                                                       |                      |                                           |

|----------------|--------------------|------------------------------------------------------------|-------------------------------------------------|----------------------|-----------------------------------------------------------------------|----------------------|-------------------------------------------|

|                | MOV<br>ABS<br>do   | A0,(x0++1),A1(X4++1) ;1<br>A0 ;1 A0=lC(i)I<br>loop_end,RPC |                                                 |                      | MOV A0,(x0++1),A1(X4++1) ;1<br>ABS A0 ;1 A0=IC(i)I<br>do loop_end,RPC |                      |                                           |

|                | MUL<br>MRD<br>BRLE | CX,A0,B1<br>CX,A1,B0<br>next                               | ;1 CX=IC(i)I*G_pot<br>;1 CX=CX-G(i)*C_opt<br>;2 |                      | MUL<br>MRD                                                            | CX,A0,B1<br>CX,A1,B0 | ;1 CX=IC(i)I*G_pot<br>;1 CX=CX-G(i)*C_opt |

|                | MOV<br>MOV         | BX,AX<br>D0,RPC                                            | ;1 C_opt,G_opt update<br>;1 keep Index          |                      | MVLE<br>MVLE                                                          | BX,AX<br>D0,RPC      | ;1 C_opt,G_opt update<br>;1 keep Index    |

| next:          | MOV                | A0,(x0++1),A1,(X4++1) ;1 next                              |                                                 | next:                | MOV                                                                   | ,,                   | 1,(X4++1) ;1 next                         |

| loop_end:      | ABS                | A0                                                         | ;1 A0=IC(i)I                                    | loop_end:            | ABS                                                                   | A0                   | ;1 A0=IC(i)I                              |

|                |                    |                                                            | 8n cycle                                        |                      |                                                                       |                      | 6n cycle                                  |

## (a)MVco(条件付き転送命令)

| 自己相関(従来品                                                           | 品)                                                                                                                                                                        | 自己相関(Hi-Perion)                                                                                                                                                                                                   |  |  |  |  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MOV<br>MOV                                                         | B0,160<br>B1,1                                                                                                                                                            | MOV B0,160<br>MOV B1,1<br>Do loop end,RPC                                                                                                                                                                         |  |  |  |  |

| loop: MOV<br>MOV<br>REP<br>MSM<br>SUB<br>SUB<br>MOV<br>MOV<br>JPC0 | RPC,B0 ;1 RPC=B0 ;1*11 A0,(X1++1),A1,(X4++1) ;1*11 RPC ;1*11 A0,(X1++1),A1,(X4++1) ;(N-k)*11 B0,B1 ;1 B0=B0-1 ;1*11 X4,B0 ;1*11 X1,X2 ;1*11 (X0++1),CX ;1*11 loop ;3*10/2 | MOV RPC2,B0 ;1 RPC2=B0 ;1*11  MOV A0,(X1++1),A1,(X4++1) ;1*11  REP2 RPC2 ;1*11  MSM A0,(X1++1),A1,(X4++1) ;(N-k)*11  SUB B0,B1 ;1 B0=B0-1 ;1*11  SUB X4,B0 ;1*11  MOV X1,X2 ;1*11  loop_end: MOV (X0++1),CX ;1*11 |  |  |  |  |

## (b)多重ループ処理(ループ内リピート処理)

| ;viterbi  |        |                       |                          |

|-----------|--------|-----------------------|--------------------------|

|           | Do     | loop_end,RPC          |                          |

|           | MOV    | B0,(x4++1)            | ;1 B0=branch tbl         |

|           | MOV    | A1,(x1++1),A0,(x5++1) | ;1 X1=Met1,X5=MetN       |

|           | ADSB   | CX,AX,B0              | ;1 C1=Met1+Bm,C0=MetN-Bm |

|           | CMLT   | C1,C0,(x6++1),D1      | ;1 cmp-sel,mem<=New_Met2 |

|           | SBAD   | DX,AX,B0              | ;1 D1=Met1-Bm,D0=MetN+Bm |

| loop_end: | CMLTD1 | ,D0(X2++1),C1         | ;1 cmp-sel,mem<=New_Met1 |

|           |        |                       |                          |

|           |        |                       | 6 cycle                  |

・拘束長=9,符号化率=1/2,データ長=192ビット/20 ms ビタビデコード処理能力約20 MIPS

#### (c)ピタピデコード

図-2 Hi-Perionコーディング例 Fig.2-Hi-Perion coding examples.

送動作になる。レジスタを介した転送の場合データの流れはレジスタが存在するALUブロックまで達する。一方,メモリ間転送の場合,データの流れはデータバスとそれに繋がるメモリのみになる。データの流れによるLSI内部の電力消費は,データ変化が多いほど消費するという観点から,メモリ間転送の方が,ストアロード転送より低消費電力動作を実現できる。

(4) 加算減算命令(ADSB/SBAD)·特殊比較命令 (CMLT/CMGT)

加算減算命令は、1組の加算と1組の減算をアキュム

レータの上位側および下位側に対して同時に行うことができる命令である。特殊比較命令は、2組のレジスタを比較し、その大小によってディスティネーション側にデータを転送することに加えて、同時に特殊レジスタ(SFTV)を1ビット左論理シフトし、比較結果の大小情報を特殊レジスタの最下位ビットに挿入する命令である。これらの命令を用いることにより、ビタビオペレーションを従来18サイクルかかっていたものを12サイクルにできた。これにより図-2(c)に示すとおり、拘束長9、符号化率1/2、データ長192ビット/20 msのビタビデコードを20 MIPS以

462 FUJITSU.49, 6, (11,1998)

#### 下で実現できる。

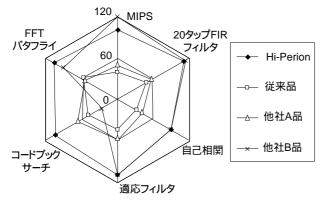

#### ベンチマーク

Hi-Perionベンチマーク結果を図-3に示す。これらは前記命令のほか,アドレス演算機能や二重転送機能,演算機能を用いて実現した値である。図において,各項目に対する性能値を結んで作られる図形の面積が性能を示し

図-3 Hi-Perionベンチマーク結果 Fig.3-Performance comparison.

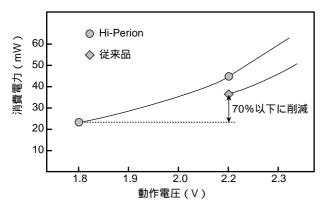

図-4 ハーフレート用PSI-CELP実行時の電力 Fig.4-Power consumption with PSI-CELP operation.

ている。この面積が大きいほど,高性能ということになる。他社相当品と比べ,携帯電話に使用される音声コーデックなどで使用される各項目に対しての性能にむらがなく高性能であることが分かる。

#### 消費電力

携帯電話に用いられるハーフレートコーデック規格のPSI-CELPを処理したときの消費電力を図-4に示す。グラフ上の結果は、Hi-PerionとPSI-CELPを処理するときに必要な周辺メモリの電力も含んでいる。Hi-PerionはDual-MACアーキテクチャを用いたことにより、積和演算能力を従来品の2倍以上にすることができた。このことが、1.8 Vという低電圧においても40 MIPS以上の動作を可能にした。40 MIPSという性能は、PSI-CELPを処理するのに十分な性能値である。従来品では2.2 V以上でないと40 MIPSという性能は出せなかった。したがって、同じ処理を行ったときの消費電力は従来品の70%以下にできたことになる。

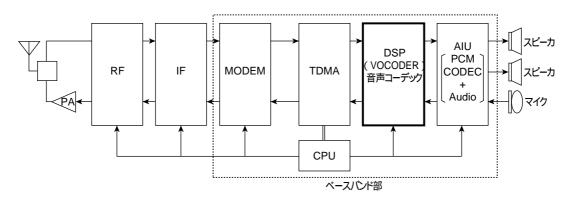

# システム応用例

携帯電話の中核を担うベースパンド部のシステム構成例を図-5に示す。本システム内においてはTDMA(時間分割プロトコル制御回路)とAIU(PCMコーデック,オーディオインタフェース回路)の間にDSPがあり,音声コーデック規格であるフルレート用VSELPとハーフレート用PSI-CELPを処理する。DSPが行う音声コーデックとは、ディジタル化された音声信号の圧縮および伸長処理である。受話器にあるマイクから入力された音声をAIUによってディジタル化し、それをDSPが圧縮データに加工し、後段のTDMAに出力する。一方、アンテナより受信された音声データはTDMAより圧縮されたデータ(チャネルデータ)としてDSPが受け取り、伸長処理を行った後AIU

図-5 PDCシステム構成図 Fig.5-PDC system configuration.

FUJITSU.49, 6, (11,1998) 463

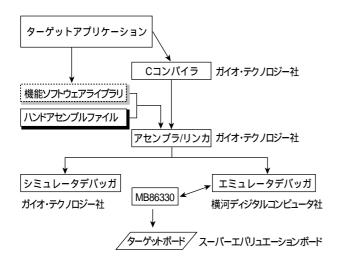

**図**-6 **開発環境** Fig.6-Development environment.

を経由して受話器にあるスピーカから音声として出力される。そのほか,エコーキャンセラ,各種ディジタルフィルタ処理などもこれらの処理を同時に行う場合がある。

## 開発環境

Hi-Perionの開発環境を図-6に示す。以下に図中に示される各ツールについて述べる。

プログラム開発用エバチップ(MB86330)

今回開発したHi-Perionをコアにしたプログラム開発用 エバチップとして,MB86330を準備した。MB86330の概 要を以下に示す。

- ・Hi-Perion(DSPコア)内蔵:16ビット固定小数点演算,最大100 MIPS

- ・メモリ構成 データRAM 8 kワード × 16 ビット テーブルRAM 16 kワード × 16 ビット 命令RAM 48 kワード × 16 ビット

- ・PCM CODEC用シリアル入出力ポート

- ・動作モード設定用シリアル入力ポート

- ・エミュレータインタフェースポート

- ・電源電圧 3.3 V単一

- ・パッケージ PGA-256ピン

- ・CMOS 0.35 μ テクノロジ

クロス環境 アセンブラ・リンカ・シミュレータデ バッガ・Cコンパイラ)

DSPファームウェア開発用ツールとしてガイオ・テクノロジー社のアセンブラ(XASS-V), リンカ(XLNK-V), シミュレータデバッガ(XDEB-V/XDBX-V)を使用できる。さらに,今後開発者からの需要が高まるCコンパイラ(XCC-V)も同社から提供されている。

#### エミュレータデバッガ

DSPファームウェアおよびDSPを組み込んだシステムデバッグツールとして横河ディジタルコンピュータ社のエミュレータデバッガ(advice)環境を使用できる。本ツールとエバチップ(MB86330)を使用することによりHi-Perionの最高性能(100 MIPS)でのデバッグが可能になる。

スーパーエバリュエーションボード

Hi-Perionに周辺回路を付加したASIC-DSPを開発したり、ターゲットアプリケーションを実現したりするDSPファームウェアのデバッグ、デモンストレーションに有効なスーパーエバリュエーションボードを開発した。本ボードは、MB86330が1個、100 KのFPGAが4個、オーディオインタフェース回路(AIU)が1個、制御ロジック、メモリなどで構成されており、エミュレータとは専用ポッド、PCとはISAバスでそれぞれ接続され、PC上の制御ソフトにより、ボード上のメモリのリードライトおよびFPGAへのダウンロード、ボード上の回路の設定などができる。本ボードを用いてN-CDMAの音声コーデック(8kQCELP)ファームウェアのデバッグ、評価およびデモンストレーションを実現した。

Hi-Perion内蔵システムLSI開発環境

Hi-Perionを内蔵したシステムLSIを開発する際に,ハードウェアで実現する部分とソフトウェアで実現する部分のパーティショニングが問題になる。この最適解をLSI試作前までに行うのが,コ・デザインである。コ・デザインでは,それぞれハードウェアモデル(RTLmodel)とファンクションモデル(Cmodel)を目的によって使い分けることで,LSI開発の期間短縮を実現できる。Hi-Perionもこのような目的に応じてRTLmodelやCmodelを準備している。RTLmodelはポータビリティを重視したマッピングし易いmodelにした。Cmodelは現在,DSP上位ツール用コアモデルライブラリとして開発中である。

#### す す が

今回開発した携帯機器向けの高性能かつ低消費電力な16ビット固定小数点DSPコア(Hi-Perion)の優れたアーキテクチャおよび開発環境について述べた。今後,市場では低消費電力化要求,高性能化要求とともにDSPコアをマクロにしたシステムLSIへの組み込み要求がより一層強くなっていくと予想される。これらの要求に対応するため,さらなる低消費電力化と性能向上を目指し,かつDSPコア内蔵システムLSI開発環境をユーザに提供するため,DSPコアモデルやDSP上流ツール用コアライブラリの開発も推進していく。

464 FUJITSU.49, 6, (11,1998)