# FRAM低電圧センス技術

## Sensing Technology for Low-Voltage Operation FRAM

### あらまし

スマートカード（マイコン、記憶回路、RF回路を搭載したICカード）に搭載されるLSIチップは、低消費電力、不揮発性、処理時間短縮のため書き換えの高速性が重要なポイントである。FRAMはこれらの要求に適した不揮発性メモリとして製品開発が進められている。LSIチップに混載されるFRAMは、周辺ロジック回路のテクノロジと同等に低電圧動作が要求されている。今回、FRAMのセンス方式として、ビット線電位をほぼGND近傍で動作させる方式を考案した。ビット線電位をGND近傍で読み出すことにより、セルに印加される読み出し電圧はビット線電位へと分圧されることなく、セルキャパシタに電源電圧相当を印加することができる。この方式により電源電圧の低下においても、効率的にセルキャパシタへの電圧印加が可能となった。

本稿では新たなセンス方式を採用した、FRAMメモリの低電圧化技術について紹介する。

### Abstract

The important requirements for Smart Card LSI chips are low power consumption, nonvolatile storage, and high-speed rewrite operation to reduce processing time. A Smart Card is an IC card that contains a microcomputer, storage circuit, and RF circuit. The ferroelectric RAM (FRAM) has been developed as a nonvolatile memory that satisfies the above requirements. An FRAM embedded in an LSI must operate as a low-voltage peripheral logic IC. We have developed a new FRAM sensing scheme that can read bit-line potentials close to the GND potential. Therefore, unlike the conventional sensing scheme, in which the voltage applied to the cell is divided into a bit-line potential and cell potential, the new sensing scheme can apply a power-supply voltage or its equivalent to the cell capacitor. This scheme allows you to efficiently apply voltage to the cell capacitor, even when the power-supply voltage is low. This paper describes a low-voltage operation FRAM that employs the new sensing scheme.

遠藤 徹（えんどう とある）

シリコンテクノロジ研究所メモリデバイス研究部 所属

現在、FRAMメモリの開発に従事。

山本 彰（やまもと あきら）

シリコンテクノロジ研究所メモリデバイス研究部 所属

現在、FRAMメモリの開発に従事。

川嶋将一郎（かわしま しょういちろう）

シリコンテクノロジ研究所メモリデバイス研究部 所属

現在、FRAMメモリの開発に従事。

## まえがき

FRAMとは、メモリセルに強誘電体を採用した不揮発性メモリデバイスである。電界を加えなくても分極を持続する強誘電体膜の残留分極特性を利用して、分極の向きを記憶データの“0”あるいは“1”として使用する。FRAMはSRAM同等の高速読み出し・書き込みが可能で、ROMと同様に不揮発性である。しかも、低消費電力であるといったことから、非接触タイプのスマートカード（マイコン、記憶回路、RF回路を搭載したICカード）に搭載されている。スマートカードは電子マネー、医療カード、アミューズメントカードなど、今後の市場拡大が予想される。

FRAMはCMOSプロセスとの整合性が良いため、スマートカードに使用されるLSIチップ上に、ロジック回路、RF回路と混載されている。今後はロジック回路の低電圧化に従いFRAM回路も低電圧動作が要求される。

本稿では、新たなセンス方式を採用した、FRAMメモリの低電圧化技術について紹介する。

## FRAMの動作原理

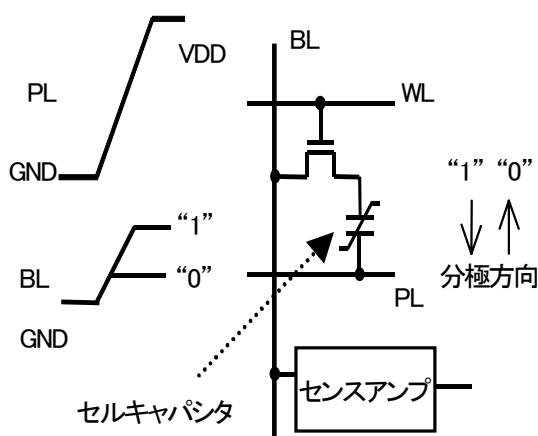

1T1C型セル（一つの強誘電体キャパシタと一つのトランジスタで構成）のFRAMメモリセル構成を図-1に示す。ワード線（WL）を選択状態にしてビット線（BL）とプレート線（PL）の間に電圧を印加すると、セルキャパシタに電圧が印加され、所定のデータ（分極方向）が書き込まれる。

“0”データを書き込む場合には $BL = 0V$ ,  $PL = VDD$ とし、“1”データを書き込む場合には $BL = VDD$ ,  $PL =$

図-1 FRAMメモリセル構造(1T1C型)

Fig.1-1T1C FRAM cell structure.

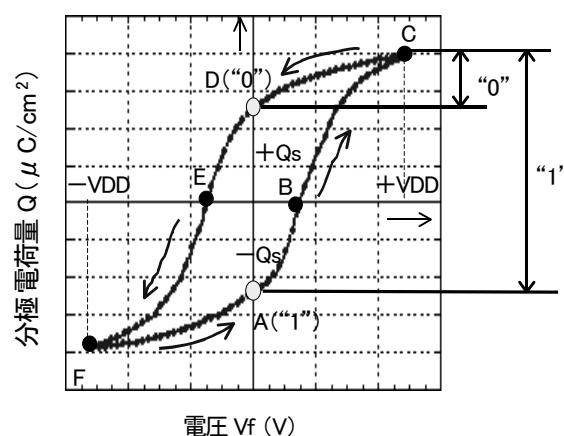

0Vとする。印加電圧により強誘電体が放出する分極電荷量Qのヒステリシス特性を図-2に示す。X軸に強誘電体キャパシタのプレート線に印加する電圧を $V_f(V)$ 、Y軸に強誘電体キャパシタの分極電荷量を $Q(\mu C/cm^2)$ とする。ここで $V_f$ の電圧を $0V + VDD$   $0V - VDD$   $0V$ と印加していくと、強誘電体の電荷はA点 B点 C点 D点 E点 F点 A点へとヒステリシス曲線を描く。印加電圧が $0V + VDD$ に変化したとき、A点 B点 C点へと変化し、強誘電体キャパシタの分極状態は反転する。一方、 $+VDD$   $0V$ と $-VDD$   $0V$ へ変化させた場合には、C点 D点への変化およびF点 A点となり、このとき強誘電体キャパシタの分極方向は反転せず、分極電荷量はわずかである。図-2のA点、D点での分極電荷量 $-Q_s$ 、 $+Q_s$ を残留分極量と呼び、A点をメモリセルの“1”データ、D点をメモリセルの“0”データに対応させる。強誘電体に印加する電圧を $0V$ （電源オフ）にしても $V_f = 0V$ で分極状態の異なるA点、D点の残留分極を持ち、データの保存が可能となる。

## FRAMの低電圧動作の課題

強誘電体メモリの“1”と“0”的センスマージンは、分極によるスイッチングの電荷量と、非スイッチングの電荷量の差 $Q_{sw}$ として検知される。十分な電荷量の差を確保するためには、キャパシタにヒステリシス曲線が飽和する電圧（C点、F点）を印加することが必要となる。

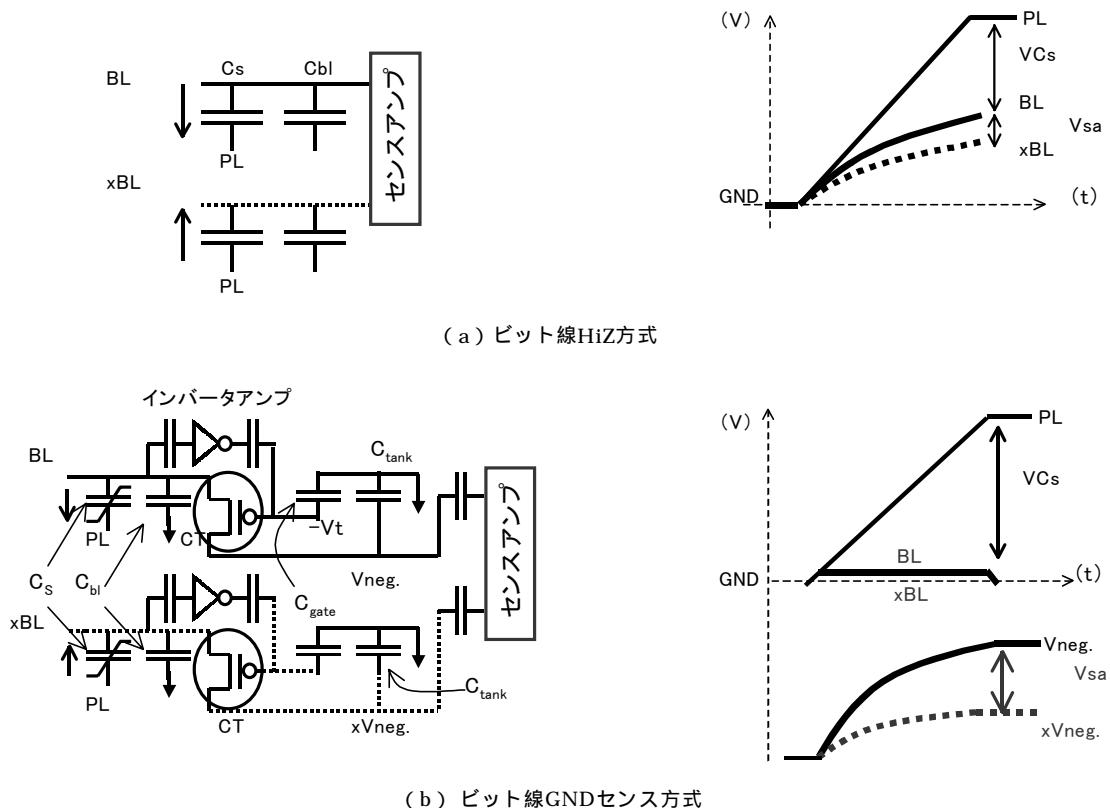

従来のビット線フローティング読み出し方式（ビット線HiZ方式）を図-3(a)に示す。フローティング読み出し方式では、セル読み出し時にプレート線（PL）に印加された電圧が、セルキャパシタ容量（ $C_s$ ）とビット線寄

図-2 ヒステリシス特性

Fig.2-Hysteresis loop.

図-3 ビット線GNDセンス方式のコンセプト

Fig.3-Bit-line GND sensing circuit (concept).

生容量 ( $C_{bl}$ ) に分圧される。このため、印加された電源電圧はセルキャパシタにそのまま印加されず、読み出しに必要なセルキャパシタ電圧の確保が不十分となる。電源電圧が5 V程度と大きな場合には、ビット線寄生容量への分圧ロス分が存在しても、セルキャパシタからの“1”と“0”的電荷を読み出すために必要な電圧は確保できている。しかし、3 V以下の低電圧動作においては、ビット線寄生容量への分圧ロスにより、セルキャパシタのデータを読み出すのに必要な電圧を確保することが困難となってくる。そこで電源電圧の低下においても十分な印加電圧を確保する読み出し方式を開発した<sup>(1)</sup>。

### ビット線GNDセンス方式のコンセプト

図-3(a)の従来のビット線HiZ方式では、セル読み出し時にはプレート線電位が上昇しビット線(BL), ビット線(xBL)にセルから電荷が流れ込む(ビット線とビット線は相補データの関係)。このとき印加されたプレート線電位はビット線容量  $C_{bl}$  とセルキャパシタ容量  $C_s$  により分圧され、ビット線電位が上昇する。このためセルキャパシタにかかる電圧  $V_{Cs}$  はプレート線に印加

された電圧より少なくなる。

つぎに今回開発したビット線GNDセンス方式を図-3(b)に示す。ビット線GNDセンス方式はビット線への電荷の供給をコントロールするチャージトランスマニア(CT)のpMOS, チャージトランスマニアpMOSのゲートに負電位  $-V_t$  を印加するための  $C_{gate}$  キャパシタ, ビット線をGND電位に固定するための負電荷蓄積用  $C_{tank}$  キャパシタで構成される。回路動作としては初めの回路リセット時に, pMOSのチャージトランスマニアのゲート電位を  $-V_t$  に初期化する。つぎに, セル読み出し時にプレート線を上昇すると, ビット線電位はGND以上となり,  $C_{tank}$ に蓄積された負電荷はpMOSのチャージトランスマニアを介してビット線に供給される。このとき, 負電荷が供給されたビット線電位はGNDに固定される。今回の試作ではpMOSはゲインが少ないプロセスであったため, インバータアンプを用いてフィードバックをかけて, ビット線をGND電位に強く固定した。こうしてビット線電位がGND近傍に固定されることにより, セルキャパシタにかかる電圧  $V_{Cs}$  はほぼ電源電圧分を確保できる。

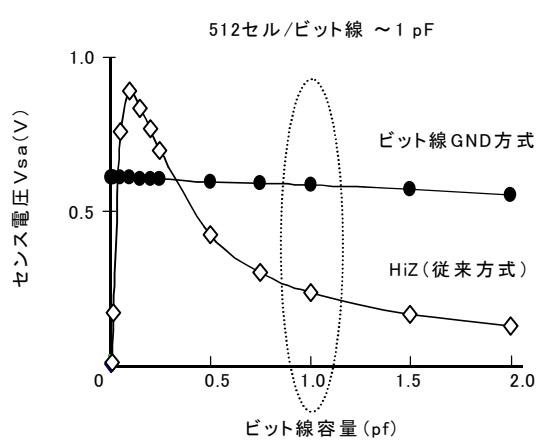

図-4 ビット線容量とセンス電圧の比較

Fig.4-Bit-line capacitance and signal amplitude comparison.

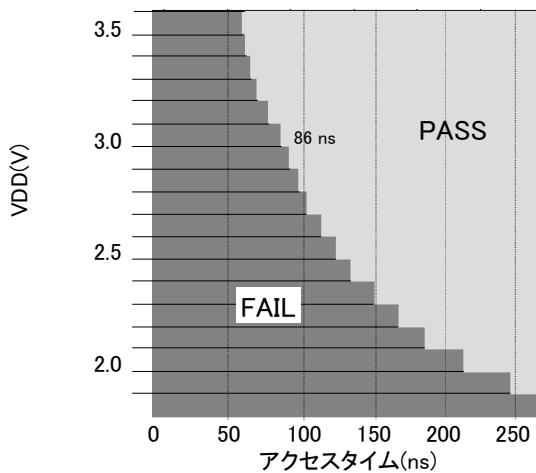

図-6 アクセスシュムー (@2MHz, 25 )

Fig.6-Measured access shmoo (@2 MHz, 25 ).

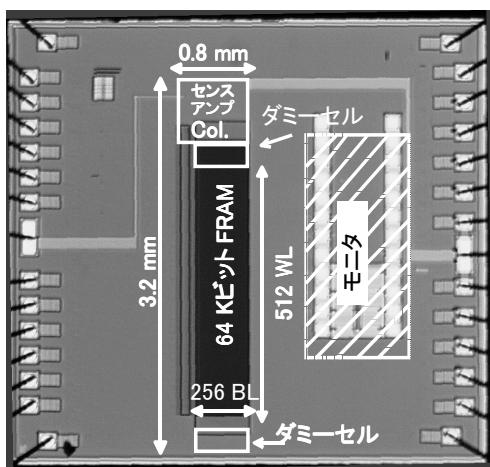

図-5 試作チップ写真

Fig.5-Chip microphotograph.

セルキャパシタからの読み出し信号の取出しは、メモリセルの“1”と“0”的電位に相当したCtankからの負電荷の供給により、Vneg上昇分を比較することによって行う。

ビット線容量と、センスアンプに供給される電圧差Vsaの関係を、従来のビット線HiZとビット線GNDセンスについて比較したシミュレーション結果を図-4に示す<sup>(2)</sup>。従来、ビット線HiZではビット線容量の増加に対してVsaはピークを持ち、その後1/Cblに近づいていく。ビット線GNDセンス方式では、ビット線容量の増加に対してVsa (VnegのBL側、xBL側の差) はほとんど一定で、最適なセンスマージンを確保するためのCbl/Cs比を気にすることなく設計ができる。今回設計した512セル/ビット線を例にとると、Cblは1 pFの点であり、こ

のときVsaはビット線HiZで0.24 V、ビット線GNDセンスで0.6 Vと2倍以上の信号差を得られる。このため、ビット線GNDセンス方式では、より低電圧でデータを読み出すことができる。さらに、ビット線GNDセンス方式は、ビット線長に依存しない設計が可能になり、今後の大容量化に向けて有効な回路手法となる。

### 試作結果

ビット線GNDセンス方式を用いた0.35 μmFRAMの試作チップ写真を図-5に示す。PZT (チタン酸ジルコン酸鉛) キャパシタサイズは $1.5 \times 1 \mu\text{m}^2$ で2T2C型のセル面積は $4.65 \times 3 \mu\text{m}^2$ である。メモリセルは512ワード×128コラムの64 Kビット FRAMで8 I/O構成である。

アクセスシュムーの測定結果を図-6に示す。試作したチップは電源電圧3 V～1.9 Vまで動作した。アクセス時間は電源電圧3 V, 2 MHz, 室温の条件で86 nsを示した。消費電力は電源電圧3 V@2 MHzの条件で6 mWであった。

### むすび

従来はプレート線に印加した電圧が、セルキャパシタとビット線に分圧されてしまい、FRAMの低電圧化の妨げとなっていた。今回試作に成功したビット線GNDセンス方式を用いることにより、電源電圧の低下に向けてもメモリセルキャパシタに電源電圧を印加できる回路方式が実現できた。低電圧動作のFRAMは、ロジックと混載することによって、スマートカードへの幅広い応用が可能である。今後は更に回路の最適化を進め、1.8 V電源電圧動作チップの開発を目指していく。

## 参考文献

- (1) S. Kawashima et al. : A Bit-Line GND Sense Technique for Low-Voltage Operation FeRAM . VLSI symposium on VLSI , 12-3 2001 . Session 12-3A .

- (2) Ali Sheikholeslami et al. : A pulse-based , parallel-

element macro model for ferroelectric capacitors . *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control* , Vol.47 , No.4 , p.784-791 ( July 2000 ).