# 携帯電話機用超微細アイソレータ の可能性

Possibility of Ultra Fine Isolator for Portable Phone

武田 茂<sup>\*</sup> 岸本 靖<sup>\*\*</sup> 伊藤博之<sup>\*\*</sup> Shigeru Takeda Yasushi Kishimoto Hiroyuki Itoh

市川耕司\*

Koji Ichikawa

携帯電話機に用いられるアイソレータの小型化と広帯域化との間にはトレードオフの関係がある。この論文では、ガーネットの寸法を一の超小型にしても、インダクター(L)とコンデンサ(C)よりなるインピーダンス変換回路を付加することにより、比帯域幅を約13%に拡大できることを独自開発の回路シミュレータの結果として紹介する。この計算結果を試す実験を、4mm角アイソレータにおいて行った。ここでLCインピーダンス変換回路はLTCC(Low Temperature Co-fired Ceramics)の積層技術を用いて作成した。この結果、836MHzで4.1%の比帯域幅を実現できた。

There is a trade-off relationship between miniaturization and specific bandwidth in an isolator for portable phone. In this paper, the new way to increase bandwidth of about 13% even with reduction of garnet dimensions by one tenth, adding the LC impedance matching circuits, has been introduced as the results of the proprietary circuit simulator. In preliminary experiments, we obtained the 4mm square isolator with 4.1% bandwidth at 836MHz using LTCC (Low Temperature Co-fired Ceramics) lamination technology.

#### ● 緒言

携帯電話機の小型化,軽量化,薄型化に伴い,これに用いられるアイソレータの小型化も急速な勢いで進行している。現在は,5mm角アイソレータが主流であるが,2GHz帯で4mm角アイソレータが市場に現れようとしている。さらに,3.5mm角や3.0mm角アイソレータの出現が将来的には期待されている。

これまで,アイソレータをどの程度まで小型化できるかという問題は,アイソレータ設計者自身だけでなく,携帯電話機器設計者の一貫した関心事の1つである。

しかし,よく言われているように,アイソレータの小型化と広帯域化はトレードオフの関係にあり,これまで両者を同時に実現することが極めて困難であった。

本論文では,独自に開発した回路シミュレータを用いてこの矛盾を解決する新しい方法を見いだしたので紹介する。

結論的に言えば,高容量コンデンサーを小型で実現できれば,売のガーネット寸法でも,LCインピーダンス整合回路を付加することにより実用に十分な帯域幅を確保できる。以下その詳細を述べる。

# ② 小型化に伴う問題点

携帯電話機用アイソレータは,三端子対集中定数型サーキュレータの一端にダミー抵抗を接続して構成される。このサーキュレータは,永久磁石でバイアス磁界が印可された円板状ガーネット,これに120度の間隔で巻かれた3つの巻線,さらに3つのコンデンサを並列接続した基本的な構造いを有する。

小型アイソレータを実現しようとすると,それぞれの要素,すなわちガーネット,永久磁石,コンデンサは当然小型にしなければならない。

サーキュレータの等価回路は、通常三端子対理想サーキュレータの各端子に並列LC共振回路が接続された形で表され、BPF (Band Pass Filter)として振る舞う。したがって、伝搬特性の帯域幅は、Lが小さくなると狭くなる。インダクタンスLは直接ガーネットの寸法に比例する。結果として、アイソレータの小型化を図るため、ガーネット寸法を小さくしていくと、狭帯域化は避けられない。

インダクタンス (L) が小さくなっても,帯域幅を一定に保つ方法はないかという問題意識が本研究の出発点

<sup>\*</sup> 日立金属株式会社 情報部品カンパニー

<sup>\*\*</sup> 日立金属株式会社 鳥取工場

<sup>\*\*\*</sup>日立金属株式会社 先端エレクトロニクス研究所

である。その答えの1つはBPFなりアイソレータの測定系の特性インピーダンス (Z) を低くすることである。例えば,帯域幅を一定にしようとすると,Lが半分の場合,Zも半分の値が要求される。このとき,動作周波数を一定に保つ必要があるので,コンデンサ (C) の値は2倍の値が要求される。

## ❸ インピーダンス整合回路

低い特性インピーダンス(Z)に適合するアイソレータが実現できたとしても、それを50 のインピーダンス(Z。)で組み立てられた実際の回路では、インピーダンス不整合のために用いることはできない。 そこで、これを用いるために、ZとZ。を結ぶインピーダンス整合回路が必要となる。もし、この整合回路の体積が大きければ、低い特性インピーダンスのアイソレータの開発は意味がない。この整合回路の小型化を図ることが超微細アイソレータを実現するための最重要課題となる。

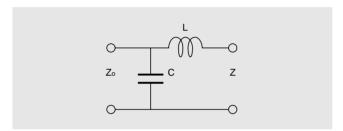

図1 インピーダンス変換回路

Fig. 1 Impedance matching circuit

このインピーダンス変換回路として我々は**図1**のようなLC整合回路を採用した。この回路の特長は,LCのみで形成され,R成分を必要としないので,本質的に無損失であることである。しかし,この回路はある特定周波数f。でのみ,実数部分のインピーダンス変換が可能であり,それ以外の周波数ではインピーダンス変換は虚数部分を発生することになる。これは一見アイソレータの帯域幅を狭くし,適当な整合回路でないように見える。ところがこの回路は,above resonanceで動作する理想サーキュレータの周波数特性と相互に打ち消し合い,逆に帯域幅を増大させることを見いだした。

まず、**図1**の整合回路の性質について述べる。ある特定周波数f。でのインピーダンス変換率Z/Z。(<1)は次のようなCとLの値のときに実現できる。

$$C^2 = (1/ Z_0)(Z_0/Z_1)[F]...(1)$$

$L^2 = (Z/)(Z_0/Z_1)[H]...(2)$

ここで, =2 f<sub>o</sub>. である。

また,  $Z/Z_{\circ}=0.5$ のとき, Lは最大値 $L_{max}$ をとり,次の式で表される。

$$L_{max} = (3979 \times 10^6) f_0 \text{ [ nH ]}....(3)$$

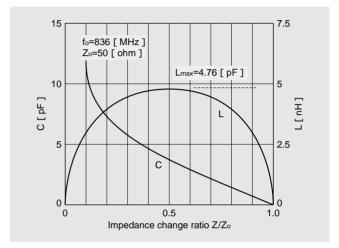

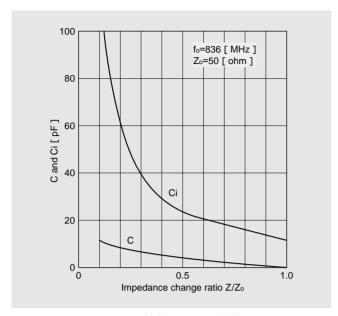

これらの関係をf₀=836 [ MHz ] について**図 2** に示した。

この図から分かるように,インダクタンス(L)は最大値 $L_{max}=4.76$  [ pF ] をとるが,コンデンサ(C) はインピーダンス変換率Z/Z。が1より小さくなっていくにつれてどんどん大きくなる。この傾向は,小型の整合回路を実現しようとする場合,好都合なことである。なぜなら,小さな空間領域に大きなインダクタンス(L)を作ることは難しいが,大きなコンデンサ(C)を作ることは比較的容易であるからである。

これは,例えば, の大きい高誘電材料を用いるとか, 積層構造を用いてその板厚を薄くし積層数を増加させる といった方法で可能である

図 2 836MHzでのCとZ/Z。の関係

Fig. 2 Relationship between C and L with Z/Z<sub>o</sub> at 836[ MHz ]

## 4 シミュレーション結果

先に報告した独自開発の回路シミュレータ $^{2)3}$ では,ガーネット寸法は空心インダクタンスKで表される。アイソレータの最適設計には,規格化動作磁界( )をほぼ = 2にすることが望ましい。動作中心周波数( $f_o$ ),外部インピーダンス(Z),ガーネットの飽和磁化4 Msが決まれば,一義的にKすなわちガーネット寸法が決まる。 $Z_o=50$  [ohm]系のKを $K_o$ とし, $Z_o$ より小さいインピーダンス(Z)のときをKとすると,を一定とすると, $K/K_o=Z/Z_o$ の関係がある。

**図1**の整合回路を付加した場合,低インピーダンスアイソレータが50 系の測定系でどのような振る舞いをするかを独自開発した回路シミュレータで調べた。

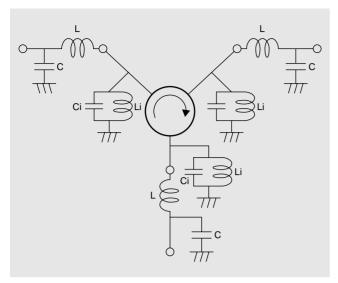

**図3**はLC整合回路を付加した場合の集中定数型サーキュレータの等価回路図である。中央部分は低インピーダンス理想3端子対サーキュレータであり,これにLC並列共振回路が接続されている。図中,Li =  $\mu$ Kの関係にある。 $\mu$ はガーネットの透磁率である。

図3 整合回路を付加した集中定数型サーキュレータの 等価回路

Fig. 3 Equivalent circuit of lumped element circulator with matching circuits

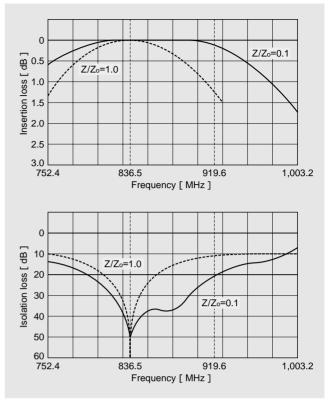

**図4**は,低インピーダンスサーキュレータに整合回路を付加した場合に,帯域幅がどの程度広がるかをSパラメータの周波数特性で見たものである。図中の点線は整合回路がない場合の計算結果である。計算の諸定数は, $f_{\circ}=836$  [ MHz ],空心インダクタンス $K_{\circ}=1.6$  [ nH ], $Z_{\circ}=50$  [ ohm ], $_{\circ}=1$  ,  $_{\circ}=0.5$  ,  $_{\circ}=0.8$  ,  $_{\circ}4$  Ms=900 [ G ] であった。この条件では, $_{\circ}=2.1$  , 比帯域幅は5.2%を得た。ただし,比帯域幅は,アイソレーションロスの20dB周波数幅で定義される。 、と、はフェライト充填( てん)率であり, は円偏波占有率である $_{\circ}$  。

これに対して、**図4**の実線はガーネット寸法を売にして,K=0.16 [ nH ] とし,50 [ ohm ] と5 [ ohm ] のインピーダンス変換回路を付加した場合のアイソレータ特性を示す。このときガーネット内部の磁界は,規格化磁界=2.1と一定にした。この図からわかるように,ガーネット寸法を売と小さくしたにもかかわらず,帯域幅は逆に広がり,アイソレーション特性は双峰特性になる。比帯域幅は約13 [ % ] と大幅に広がった。帯域幅の広がり方は,f。に対して高周波側に広がるのが特長である。

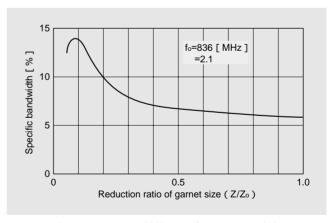

図5は,上記の関係を種々のインピーダンス変換率について計算し,それらをまとめて,横軸をインピーダンス変換率にとり,縦軸を比帯域幅をとったものである。内部磁界 =2.1は一定になるようにした。帯域幅は,インピーダンス変換率が小さくなるにつれて,漸増し, $\frac{1}{10}$ でピークをとる。このときの整合回路の定数は, $\frac{1}{10}$ に用], $\frac{1}{10}$ に下頭著である。

図 6 は、インピーダンス変換率に対する低インピーダンスサーキュレータの並列LC共振回路のコンデンサ(Ci)の変化を示す。CiはZ/Z。に反比例して大きくなる。特に、 $Z/Z_0$ =0.1では、Cは100 [ pF ] 以上必要であり、これをいかにして小型化するかが課題である。

図4 回路シミュレータにより計算したガーネット寸法縮小による帯域幅増加効果

Fig. 4 Broadening effect of bandwidth with garnet size reduction obtained by circuit simulation

図5 回路シミュレータで計算したガーネットの寸法縮小率と帯域幅の関係

Fig. 5 Change of bandwidth with garnet size reduction obtained by circuit simulation

### ⑤ 実験結果

上記は回路シミュレータで得られた結果である。これ を実証するために、セラミック低温焼成技術(LTCC)

図 6 836MHzでのZ/Z。に対するCとCiの関係

Fig. 6 Relationship between C and Ci with Z/Z<sub>o</sub> at 836[ MHz ]

を用いてインピーダンス変換回路を製作し,4mm角アイソレータにおいて予備的な実験を行った。

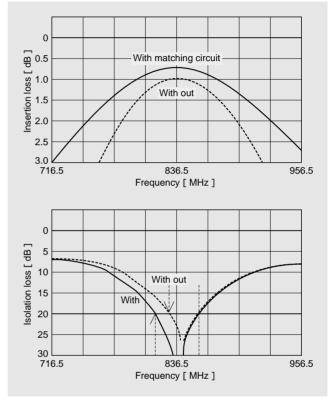

4mm角アイソレータでは,大きなガーネット寸法を内蔵できず2.2mm 程度が限界である。このガーネットを用いて,整合回路なしで50[ohm]に整合するように作成した場合,**図7**の点線のように,比帯域幅は2.7%とかなり狭いものしか得られなかった。

これに対して,セラミック低温焼成技術(LTCC)を用いて,50 [ohm] と37.4 [ohm] のインピーダンス変換回路(L=4.1 [nH], C=2.2 [pF])を付加した場合は,**図7**の実線に示すように,4.1%まで帯域幅が大幅に拡大した。同時に,挿入損失も改善されている。

整合回路がない場合に挿入損失が大きいのは,内部磁界が強くなりすぎ,コンデンサ(C)が大きくなり,その放電電流により,中心導体の導体損失の効果が顕著となるからである。整合回路を付けた場合に損失が減少したのは,内部磁界が減少し,導体損失が減少したためと考えられる。しかし,挿入損失のピーク値は0.7dBで,通常の5mm角アイソレータの0.3dBと比較すると2倍以上あり,実用に供するレベルにない。この損失のほとんどは整合回路によるものであり,より低損失のLC回路の作成が課題である。

### 6 結 言

携帯電話機用アイソレータの超微細構造を実現するための新しい方法を紹介した。この方法を用いると,ガーネット寸法を売にしても,内部インピーダンスを売にするLCインピーダンス変換回路を付加すると,約13%の比帯域幅が得られるることを回路シミュレータにより確認した。

これを実証するための予備実験として、836MHz帯の4mm角アイソレータにおいて、LTCC技術で作成したインピーダンス変換回路を内蔵し、比帯域4.1%を実現した。これにより、ほぼ理論どおりの現象が生じていると

図7 整合回路がある場合とない場合の4mm角アイソレータ の予備実験結果

Fig. 7 Preliminary experimental results of 4 mm square isolator with and without matching circuits

# 参考文献

- 1) Y.Konishi: IEEE MTT-13, pp852-864 (1965)

- 2 ) S.Takeda: 1998 IEEE MTT-S Digest, pp 621-624 (WE2E-2)

- 3 ) S.Takeda: 1999 IEEE MTT-S Digest, pp 1361-1364 (WEF3-1)

- 4) S.Takeda: 2001 IEEE MTT-S Digest, pp 479-482 (TUIF-21)