# 室温動作单電子トランジスタの動特性に関する研究

白 横 淳 一 秋田県立大学システム科学技術学部助教授

## 1. 研究の目的

1947年に発明されたトランジスタは今日のエレクトロニクス社会を実現させ、その趨勢はますます加速している。人類の飽くなき欲求は情報処理量の爆発的な増加を招き、それに対応する形で電気通信／情報処理技術の超高速・大容量化が達成されてきたが、地球のエネルギー資源は有限であり、電気通信／情報処理に振り分けられるエネルギー量にも自ずと限界があることもまた事実である。この有限のエネルギーのもとでより多くの情報を処理するには、1ビットあたりの処理に要するエネルギー量がより小さい情報処理デバイスの実現が必須である。仮に情報処理デバイスのオン・オフ状態のエネルギー差として1ビットあたりのエネルギーを定義するならば、現在の高性能なCMOS論理回路では約 $10^5$  eVとなる。これから環境調和型社会では、人間は有限の資源を如何に浪費せずに知的文化的な生活を送ることが可能であるかを問われる時代である。この様な観点から、低消費電力化はまさに次世代技術の本流であり、1ビットを如何に低エネルギーで表現出来るかという低消費電力技術が電気通信／情報処理において重要なのは明らかである。

本研究ではこのような現状認識に基づき、ビットあたりのエネルギーが約1eV或いはそれ以下であるような情報処理デバイスの開発を目的としている。具体的には、单電子帯電効果を基礎とする、電子1個で動作可能な单電子トランジスタの開発とその室温動作化の達成、さらに1～数10個程度の電子で1ビットの記憶・論理演算を可能とするような室温動作单電子トランジスタシステムの開発を行う。この单電子素子は、情報処理デバイスの行き着く極限の姿を示唆しており、次世代の電気通信技術・情報処理技術を支え得る可能性を明らかにする意義は大きいものと考えられる。

## 2. 单電子トランジスタの室温動作

近年の半導体極微細加工プロセス技術や結晶成長技術の目覚ましい発展は、单電子帯電効果を基礎とする新しいエレクトロニクスを開花させつつある。この单電子エレクトロニクスの基本素子であり、クーロンブロックード現象をその動作原理とする单電子トランジスタ（SET）は、半導体材料や金属材料を舞台として研究が進展している。クーロンブロックード現象とはトンネル接合の微細化において顕著な帯電効果であり、1つの電子がトンネル障壁を通り抜けることでその両端にある金属電極が静電的に帯電し、系の静電エネルギーが増加することで（外部からその増加分のエネルギーが与えられない限り）電子のトンネルが抑制される現象である。この静電エネルギーは系の静電容量に反比例するため、仮に非常に微細な（静電容量の小さな）トンネル接合が作製出来るならば、クーロンブロックード現象が観測可能な温度範囲も上昇することを意味している。

このように、单電子素子とは素子の微細化が動作温度の向上と直接的に結びついている事が特徴であり、言い換ればトンネル接合の微細化なくして動作温度の向上は望めない。このような観点から、素子微細化は室温動作を実現させるために極めて重要な課題であり、主に電子線リソグラフィー技術によりその微細化が進められてきた。しかし近年においては、走査型トンネル顕微鏡（STM）や原子間力顕微鏡（AFM）等の走査型プローブ顕微鏡（SPM）技術が急速な発展を遂げ、これらは単なる表面観察用ツールのみならず、原子をも操れる分解能を有する超微細加工ツールとしての一面が注目され始めている。

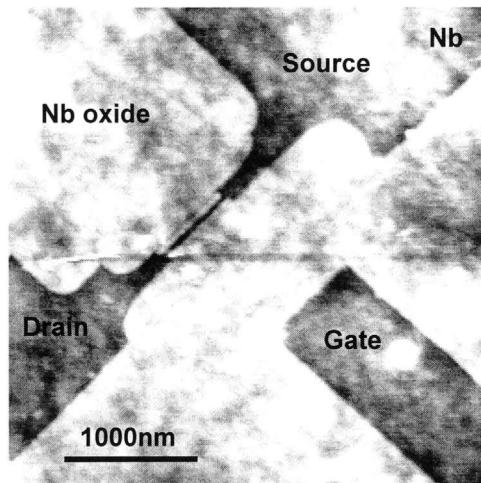

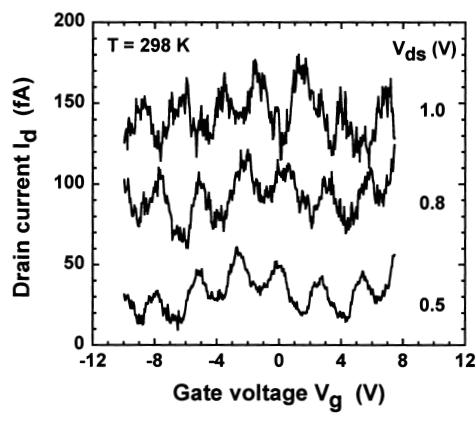

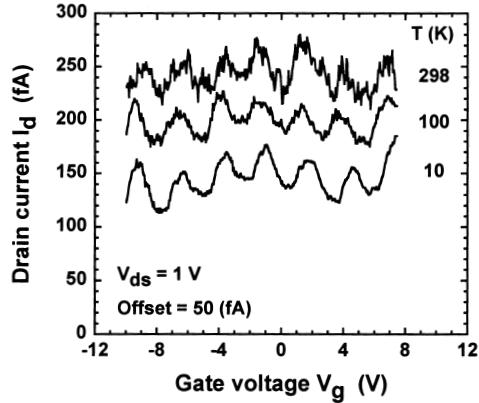

本研究テーマでは、これまでに原子オーダーの分解能を有するSTMやAFM等のSPM探針を陰極とし、陽極酸化反応により金属極薄膜に対してnmオーダーの選択酸化を行うSPM超微細酸化法を開発した。更に、（SPM超微細酸化法と組み合わせることでその微細化限界を越える事が可能）新しい微細構造作製手法である熱酸化法を開発した。これらの手法をニオブ（Nb）極薄膜に適用し、非常に微細なNb／酸化Nbトンネル接合を有するNb系SETを作製した結果、室温に於いてクーロンブロックード電圧の変調特性やクーロンブロックード振動特性を観測し、单電子帯電効果を確認することに成功した。図1には実際に作製したNb系SETのAFM像を示す。この構造ではソース、ドレイン、ゲートが同一平面上にあり（プレナー型）、サイドゲート構造を有している。また、図2はNb系SETでの室温動作特性を示している。

図1 室温動作Nb系SETのAFM像

(a) パラメータ：ドレイン電圧

(b) パラメータ：動作温度

図2 Nb系SETのドレイン電流 ゲート電圧特性

### 3. 室温動作单電子トランジスタを用いた回路シミュレーション

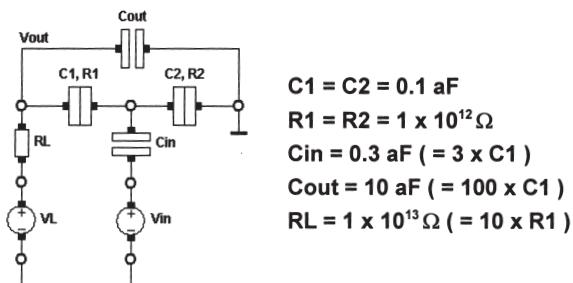

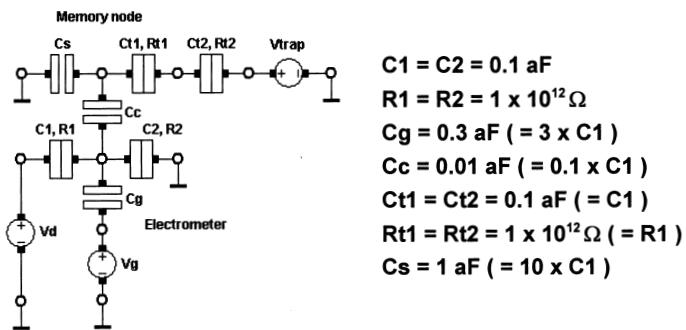

新しい電子素子であるSETを用いた論理・記憶回路システムを実現する研究に於いては、nmオーダーの非常に微細な素子構造を制御性良く作製しなければならず、その作製の困難さから実験面での動作確認は容易ではない。そこで、実験で得られたSET単体の各種素子パラメータを利用した、計算機による回路特性の予測が非常に重要な研究課題となってくる。本助成期間内では、既に開発済みの室温動作SETから、シミュレーションに必要なトンネル接合の各種パラメータ（トンネル接合抵抗値、トンネル接合容量値等）をオーソドックス理論とのフィッティングにより抽出し、その

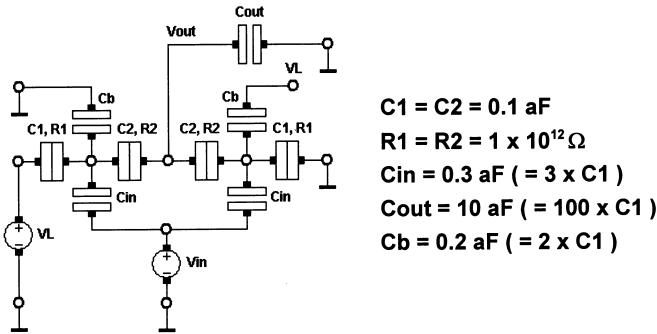

パラメータを用いてモンテカルロ法による回路シミュレーションを行った。本研究で作製した室温動作SETから抽出された典型的な素子パラメータは、トンネル接合容量：0.1aF、トンネル接合抵抗： $1 \times 10^{12} \Omega$ 、ゲート容量：0.3aFであり、帯電エネルギーは300meV程度である。

#### 4. 室温動作SET論理回路

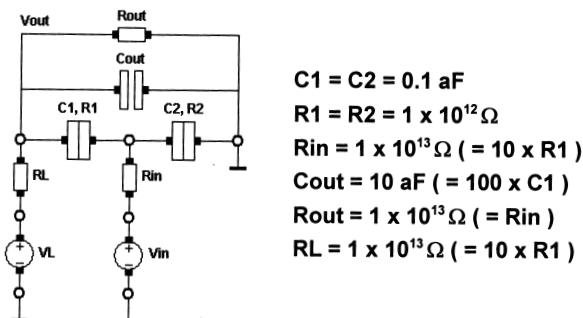

##### 4.1 容量結合型SETインバータ

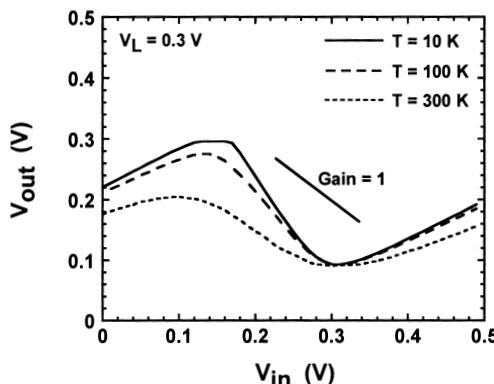

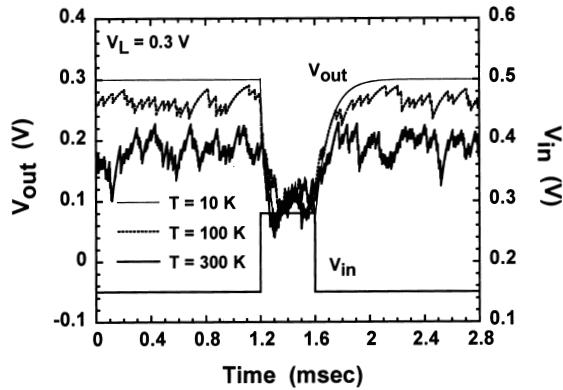

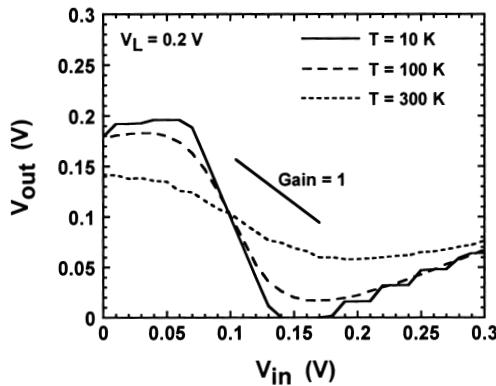

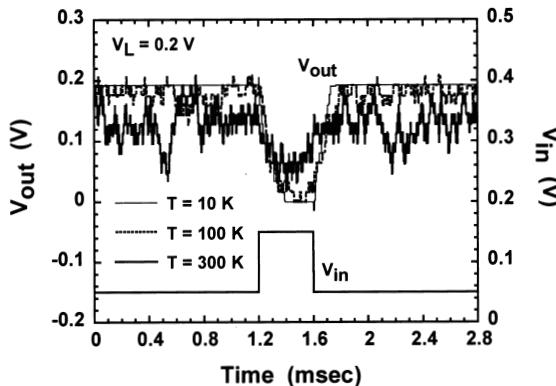

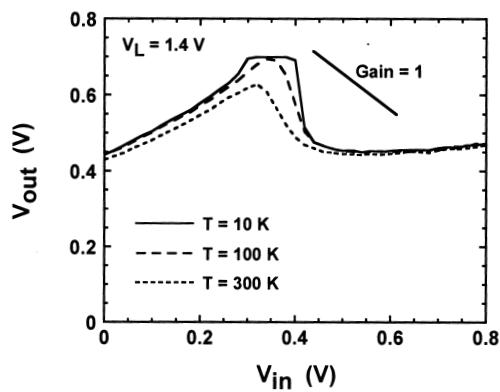

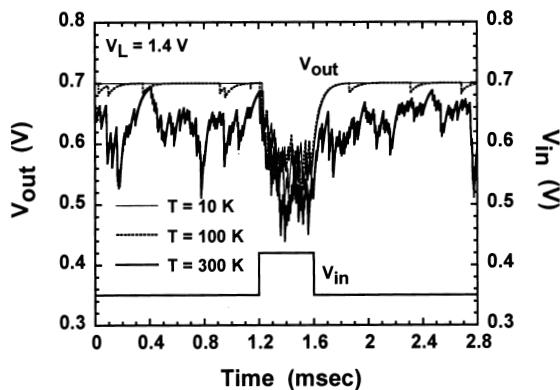

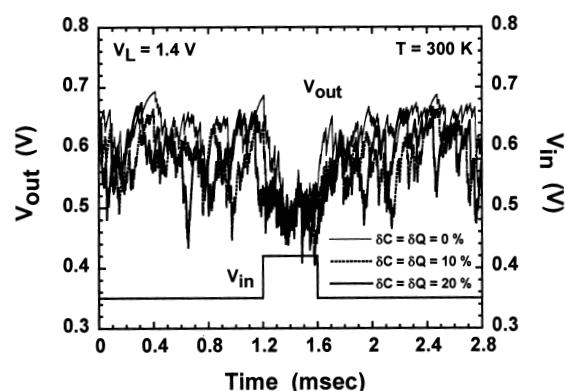

図3に容量結合型SET（C-SET）インバータ回路を示す。この回路では10aFの負荷容量を接続し、18個の電子の有無で1ビットを表現しており、また、ビットあたりのエネルギーは約1eVとなっている。図4はC-SETインバータ回路の伝達特性を示している。これより、動作温度が100K以下では、入力電圧 $V_{in}$ が0.15~0.3Vの範囲でその電圧利得は1以上となっている。しかし、動作温度が300Kになると電圧利得は1以下となり、入力電圧の振幅に対して出力電圧の振幅が小さくなるため、300Kでのスイッチング特性を利用する際には設計上の注意を要する。また、図5は同一回路でのスイッチング特性を計算したものである。これより、動作温度が10Kでは明瞭なインバータ特性を示しているが、10K以上の温度では熱的に励起されたトンネル電子の影響により、出力電圧 $V_{out}$ は電子のトンネル過程の確率的な特徴を反映した電圧振動を示している。300Kに於いても出力電圧のスイッチング特性は確認できるが、図4にも示されているように電圧利得は1以下となり、動作マージンも大幅に狭くなることがわかる。

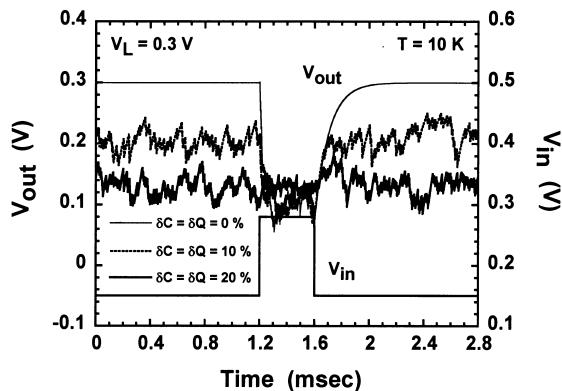

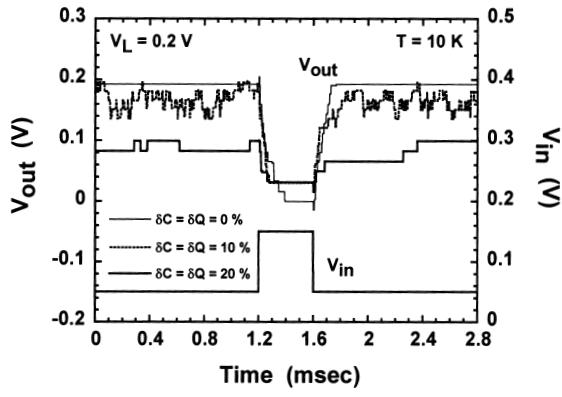

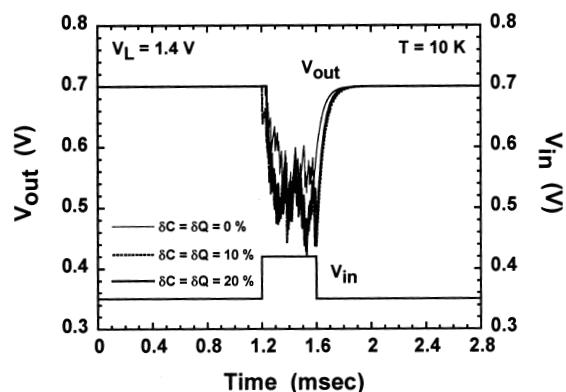

図5の特性では、トンネル接合周辺部には一切の背景電荷（固定電荷）は存在しないとし、また、トンネル接合パラメータも全てのトンネル接合で同一と仮定している。しかし、実際にはこの様ないわば「クリーン」な系は存在せず、より現実に近い回路シミュレーションには背景電荷の揺らぎやトンネル接合の製作上のばらつきから生じるトンネル接合容量やトンネル接合抵抗の揺らぎを盛り込んだ「ダーティ」な系での現実に即した検討が必要とされる。実際に、この「ダーティ」な効果を取り込んで初期的な検討を行った結果を図6に示す。ここでは、動作温度を10Kとし、C-SETインバータ回路の全てのノードに0~20%の電荷揺らぎを与え、同時に、全てのトンネル接合や容量に0~20%の容量揺らぎを与えている。これより、背景電荷やトンネル接合の接合パラメータが10~20%以上の揺らぎを示すと（この揺らぎが0%の時が「クリーン」な状態）、C-SETインバータ回路における動作バイアス点がこの揺らぎにより変動してしまい、出力電圧におけるスイッチング波形の論理振幅が定義できなくなることが明らかとなった。これは10Kでの結果であるが、更に温度を上げれば熱励起されたトンネル電子の雑音が重畠されてくるため、300Kではスイッチング動作の確認は非常に困難になるものと思われる。一般に、C-SETは電荷分解能が高すぎるために周囲の電荷揺らぎによる影響を敏感に受け易く、C-SETの回路応用にはこれらの影響を考慮した回路構成法を構築する必要があるものと思われる。

図3 C-SETインバータ

図4 C-SETインバータの伝達特性

図5 C-SETインバータのスイッチング特性(揺らぎ無し)

図6 C-SETインバータのスイッチング特性(揺らぎ有り)

#### 4.2 相補型SETインバータ

図3に示したC-SETインバータは負荷として抵抗を用いた回路形式であるが、消費電力やゲート回路の時定数を考慮すると抵抗負荷ではなく、SETを負荷とした回路形式が望ましい。そのような観点から、一般的な半導体メモリ技術に於ける相補型MOSインバータ(CMOSインバータ)にならい、室温動作SETを負荷に用いた相補型SET(Complementary-SET)インバタ回路を提案し、その動作特性について検討した。

図7に相補型SETインバタ回路を示す。ここでは10aFの負荷容量を接続し、1ビットを12個の電子で表現している。図8は相補型SETインバタ回路の伝達特性を示している。入力電圧が0.07~0.13Vの範囲に於いて、動作温度が300Kでは電圧利得は1以下となってしまうが、100K以下では1以上の利得が得られる。また、相補型の回路構成であるために、スイッチングSETがONの際には負荷SETはOFFとなり、そのOFF状態はクーロンブロッケードにより規定されることから、OFF状態での負荷SETの抵抗は非常に大きくなる。このため、伝達特性での遷移幅は、C-SETインバタ(図4)と比較すると相補型SETインバタの方がより小さくなり、電圧利得をより大きくすることが出来る。図9は、背景電荷とトンネル接合容量の揺らぎを考慮しない条件下でのスイッチング特性を計算したものである。出力電圧の温度依存性は先のC-SETインバタの場合とほとんど同じであり、300Kに於いてもスイッチング特性の確認は可能であるが、電圧利得はやはり低下しており、1以下となっている。また、熱励起トンネル電子による電圧振動もC-SETインバタと同様に発生している。更に、背景電荷とトンネル接合容量の揺らぎを0~20%と考慮した際の結果を図10に示す。(a)は動作温度が10K、(b)は300Kの時の結果を示している。これより、10Kの時には、10%程度の揺らぎ要因に対してはC-SETインバタと比較してより強い耐性を示している。しかし20%程度の揺らぎに対しては、やはり出力電圧の論理振幅を定義することは難しい。動作温度が300Kの際には、揺らぎ要因が10%以上でもはやスイッチング動作の定義是不可能となっている。これは、SET単体で室温動作が可能であっても、それを用いて相補型SETインバタ回路を構成した際には、結果として系全体の静電容量成分が大きくなり、回路としての室温動作条件を満足することが出来なくなることを意味している。回路の室温動作を満足させるには、より大きな帯電エネルギーを有するSET単体が必要であり、それを加味した回路設計が重要になってくる。

図7 相補型SETインバータ

図8 相補型SETインバータの伝達特性

図9 相補型SETインバータのスイッチング特性（揺らぎ無し）

#### 4.3 抵抗結合型SETインバータ

これまでに検討したC-SETインバータ回路や相補型SETインバータ回路では、C-SETがその基本素子となっていた。C-SETでは2つのトンネル接合に挟まれたアイランド電極が、ゲート電極に対して静電的に結合しており、ゲートに印加する電圧でアイランド内の電荷数を制御している。そのため、クーロンブロッケード状態はアイランド内の電荷数に対して周期的に振る舞い、且つ、その状態を変化させるために必要な電荷数は1電子電荷以下という超高電荷分解能を有している。このような特性は、電荷を検知する電荷計という観点からは有利な特徴であるが、反面、ほんの僅かな電荷数の変化がその特性に大きく影響を及ぼし得る、と見ることもできる。このようなC-SETを論理ゲート回路として応用した場合には、背景電荷やトンネル接合容量の揺らぎがその特性に多大な影響を与えていた。ここでは、動作原理的に背景電荷の影響がない抵抗結合型SET (R-SET) を基本素子とした、R-SETインバータ回路について検討を行う。R-SETでは、アイランド電極がゲート電極と抵抗により結合されており、アイランド内の余分な電荷数はゲート抵抗を通して緩和されるためにクーロンブロッケード状態は一義的に定まり、アイランド電荷数に対して周期的に振る舞うことない。これは即ち、R-SETインバータ回路では、その特性は背景電荷の揺らぎには何ら影響されないことを意味している。

(a)  $T = 10\text{K}$ (b)  $T = 300\text{K}$

図10 相補型SETインバータのスイッチング特性（揺らぎ有り）

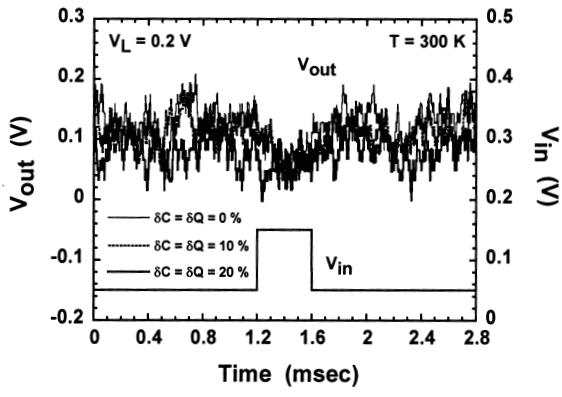

図11にR-SETインバタ回路を示す。また、図12はその伝達特性を計算したものである。これより、入力電圧が0.4V付近での電圧利得は非常に大きいことがわかり、300Kに於いても尚、1以上の利得が得られている。図13は全ての揺らぎ成分を無視した場合のR-SETインバタに於けるスイッチング特性を計算したものである。スイッチング特性は300Kに於いても確認することが出来、且つ、その利得も1以上であることがわかる。また、100Kでのスイッチング特性に注目すれば、C-SETインバタ（図5）や相補型SETインバタ（図9）の場合と比較して、その安定性の向上が確認できる。更に、図14は0~20%の揺らぎ成分を考慮に入れたスイッチング特性を示しており、(a)は10K動作、(b)は300K動作を示している。これより、10Kに於いては、背景電荷揺らぎやトンネル接合容量の揺らぎが20%になってしまって、揺らぎがない場合と殆ど同じ特性を示すことが明らかとなった。また、300Kの場合には、熱励起トンネル電子によるノイズは生じているが、20%の揺らぎがあっても尚、スイッチング特性を定義できることが明らかとなった。これは、C-SETをベースとしたインバタ回路と大きく異なり、R-SETの電荷揺らぎに対する非干渉性と、R-SET単体の帯電エネルギーの向上が、回路の室温動作に於ける安定性向上に寄与したものと考えることが出来る。

図11 R-SETインバタ

図12 R-SETインバータの伝達特性

図13 R-SETインバータのスイッチング特性(揺らぎ無し)

(a)  $T = 10K$

(b)  $T = 300K$

図14 R-SETインバータのスイッチング特性(揺らぎ有り)

## 5. 室温動作SET記憶回路

### 5.1 単電子トラップメモリ

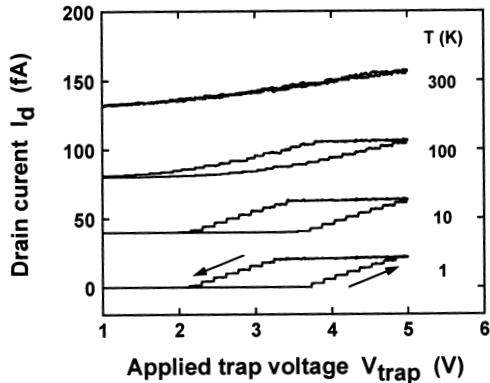

単電子のトンネル現象をメモリへ応用する基本的な方法は、1ビットを1つの電子で表現することである。図15は、室温動作SETを用いた単電子トラップメモリを示している。これは、電子を蓄えるトラップ電極が2重トンネル接合を介して接続されており、トラップ電圧を変化させることでトラップ電極に電子が捕獲されていない状態（“0”状態）から、捕獲されている状態（“1”状態）へと変化させることが出来る。これらの2状態は、トラップ電極をSETに静電的に結合させ、SETの電流変化という形で非破壊的に読み出すことが可能である。

図16はトラップ電圧を0~5Vとスイープさせた時の、SETのドレイン電流の変化を計算したものである。これより、動作温度が100K以下に於いては明瞭なヒステリシス特性が現れており、この双安定状態を“0”と“1”に対応させることで単電子トラップメモリとして用いることが出来る。しかし、動作温度が300Kになると、今回の計算に用いたパラメータでは双安定状態は消失してしまう。動作温度を上げるためににはSET単体の帯電エネルギーを単純に増加させるだけではなく、論理回路の場合と同じく、SET単体では室温動作が可能でも、メモリの動作温度は系全体での静電容量成分によりスケールされるため、回路機能を踏まえたSET単体の設計がやはり重要となってくる。

図15 単電子トラップメモリ

図16 メモリ動作

### 5.2 単電子フラッシュメモリ

単電子トラップメモリの結果を見てもわかる通り、帯電エネルギーのみで電子をトラップ電極内に捕獲して保持するメモリ回路構成では、動作温度がSETの帯電エネルギーとほぼ同等ではトラップされている電子は逃げてしまい、メモリ動作は示さなくなってしまう。そこで、より高温動作が可能で、記憶保持時間の長いメモリ回路を検討する目的から、既存の半導体メモリ技術に於ける不揮発性メモリとの類似性にならって、フラッシュメモリの単電子動作版を検討してみる。

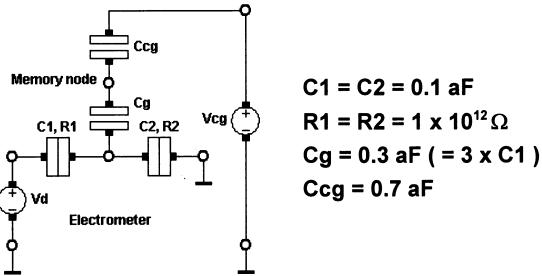

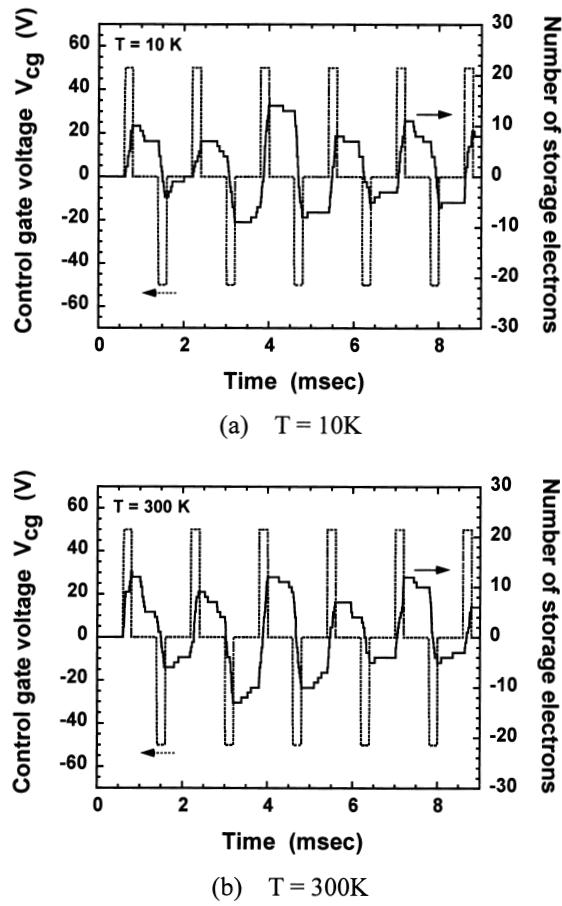

図17は単電子フラッシュメモリを示している。ここでは、電子を捕獲・保持する浮遊記憶ノードがあり、それが静電的にSETに結合され、SETを単電子電荷計として用いることで記憶された電子の読み出しを行う。また、浮遊記憶ノードへの電子の注入にはFNトンネリングを用いている。図18は、10K(a)と300K(b)でのメモリ動作を計算したものである。これより、10Kでの動作に注目すると、50Vの入力書き込み電圧が印加されると8~14個の電子が書き込まれ、入力を切ってもその電子数はほぼ保持されており、1ビットを8~14個の電子で表現する不揮発性のメモリ回路として動作していることがわかる。他方、-50Vの消去電圧により、書き込まれた電子を消去することも可能である。この50Vでの書き込

み・消去モードでは、約 $200\mu\text{s}$ の書き込み・消去時間を得ている。また、300Kでの動作では、書き込まれた電子の保持特性に於いて、熱励起により電子数が減少する傾向が生じているものの、保持される電子数や動作速度は低温での動作の場合とほぼ同じである。これより、単なる静電エネルギーだけで無く、浮遊記憶ノードでの非常に大きな時定数で電子を閉じこめるタイプの单電子フラッシュメモリでは、室温動作の可能性が明らかとなった。

図17 単電子フラッシュメモリ

図18 メモリ動作

## 6. 室温動作SETアナログ回路

これまで室温動作SETを論理回路へ応用した、いわばデジタル的な側面からその回路の特徴について調べてきたが、ここでは室温動作SETの入力に定常交流振幅を加えた際の出力、即ちアナログ的な回路応用について検討を加える。基本的な回路構成は図3に示したものと変化はなく、図4の伝達特性において電圧利得が1以上の条件となるようなバイアス点として $V_{in}$ を設定し、そのバイアス点を中心に交流振幅を加えた際の出力特性について検討した。

動作温度10Kに於いて、交流振幅として入力に三角波を加えた際の入出力電圧特性を計算した結果、入力信号の逆位相で出力が増幅されることが明らかとなった。この様に、適切な入力動作バイアス点を設定することで、入力信号の増幅というアナログ的な回路動作が可能であることが明らかとなった。但し、図4の伝達特性では動作温度が300Kとな

るとその電圧利得は1以下となってしまうことから、単電子トランジスタを300Kにおいてアナログ的に応用するには、電圧利得を大きく取れる回路構成の検討が重要となってくる。この様な意味からも、相補型SETや、R-SETを用いた回路構成が重要なものと思われる。

## 7. まとめ

本研究でのこれまでの成果として、既に、原子や分子を操作することが可能なSPMを微細構造作製装置として用いる事で、従来手法では達成不可能であった数nmの微細構造を制御性良く作製する手法を確立している。更に、本手法を用いることで、材料としてNbを採用したNb系SETを作製し、室温動作を達成することに成功している。本研究助成に於いては、この様な先駆的な研究成果を背景とし、集積化された室温動作SETシステム実現に向けての様々な回路構成についての理論的な検討を中心に行った。

室温動作SET論理回路では、C-SETインバータ・相補型SETインバータ・R-SETインバータ回路について、各種の揺らぎ要因に対する耐性や動作温度という観点から検討を行った。室温動作SETを用いたインバータ回路を室温にて動作させるには、R-SETインバータ、相補型SETインバータ、C-SETインバータ、の回路構成順に有利なことが明らかとなった。

また、室温動作SET記憶回路では、単電子トラップメモリ・単電子フラッシュメモリ回路について、動作温度の観点から検討を行った。室温にてメモリ回路を実現するには、単電子フラッシュメモリ、単電子トラップメモリ、の回路構成順に有利であることが明らかとなった。

更に、室温動作SETの入力に定常交流振幅を加えた際の出力、即ちアナログ的な回路応用について検討を加えた結果、適切な入力動作バイアス点を設定することで、入力信号の増幅というアナログ的な回路動作が可能であることが明らかとなった。今後はこれらの結果をもとにして、実際の回路作製による検討を行う予定である。

## 謝辞

最後に、本研究を遂行するに当たり多大なご助成を賜りました電気通信普及財団に感謝申し上げます。

## < 発 表 資 料 >

| 題 名                                                                                                 | 掲載誌・学会名等                                                                                                       | 発表年月     |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------|

| Room Temperature Operation of Nb-Based Single-Electron Transistors (Invited)                        | 4th International Conference on Thin Film Physics and Applications (2000TFPA), May8-11, 2000, Shanghai, China. | 2000年5月  |

| Room Temperature Operation of Nb-Based Single-Electron Transistors (Invited)                        | Proc. SPIE Vol. 4086 (2000) 317-322.                                                                           | 2000年11月 |

| TMR on ferromagnetic single-electron transistors with multiple tunnel junction                      | 8th Joint MMM-Intermag Conference, January 7-11, 2001, San Antonio, Texas, USA.                                | 2001年1月  |

| 強磁性多重トンネル接合単電子トランジスタ                                                                                | 日本応用磁気学会誌 第25巻 第4-2号 (2001) 783-786.                                                                           | 2001年4月  |

| Tunnel Magnetoresistance on Ferromagnetic Single-Electron Transistors with Multiple Tunnel Junction | J. Appl. Phys., Vol. 89 (2001) 7365-7367.                                                                      | 2001年6月  |